# **ECE 120: Introduction to Computing Fall 2024 – Final Exam**

Friday, December 13, 2024

- Ensure that your exam booklet has 15 pages and additional four pages of formula sheets + scratch paper.

- Please, write your NAME, NetID, and UIN clearly.

- Do not tear the exam booklet apart. You can only detach the scratch paper and the formula sheet if needed.

- This is a closed book/notes exam. You may use a calculator.

- You are allowed **one handwritten sheet** of notes (both sides). Write your name on the cheat sheet. The cheat sheet will be collected at the end of your exam.

- Absolutely no interaction between students is allowed.

- Clearly indicate any assumptions that you make.

- The questions are not weighted equally. Budget your time accordingly.

- Show your work and write legibly. Solutions in illegible handwriting will be graded as incorrect.

- Write your UIN (9-digit #) on each page in the provided space.

| NAME  | ANSWER    | R KEY      |     |

|-------|-----------|------------|-----|

|       |           |            |     |

| NetID |           |            | UIN |

|       |           |            |     |

|       | Problem 1 | 10 points  |     |

|       | Problem 2 | 15 points  |     |

|       | Problem 3 | 24 points  |     |

|       | Problem 4 | 10 points  |     |

|       | Problem 5 | 24 points  |     |

|       | Problem 6 | 7 points   |     |

|       | Problem 7 | 10 points  |     |

|       |           |            |     |

|       | Total     | 100 points |     |

|--|

## **Problem 1 (10 points): Binary Representation and Operations**

| 1. | <b>(2 points)</b> The current version of Prof. Lumetta's ECE 120 lecture notes is 170 pages long. Prof. Lumetta decided to refer to each page using fixed-length binary words, what is th <b>minimum number of bits</b> needed per page? |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Minimum number of bits: (decimal number)                                                                                                                                                                                                 |

|    | How many additional pages can Prof. Lumetta add to his lecture notes while keeping the same number of bits?                                                                                                                              |

|    | Additional number of pages: (decimal number)                                                                                                                                                                                             |

| 2. | (2 points) Perform the following bitwise logical operations.                                                                                                                                                                             |

|    | <b>a.</b> 0010 NAND 0011 = (binary)                                                                                                                                                                                                      |

|    | <b>b.</b> 1001 XOR ( NOT(0011) ) = (binary)                                                                                                                                                                                              |

| 3. | (3 points) Perform the following operation in 4-bit 2's complement representation.                                                                                                                                                       |

|    | 1010 – 1110 = (binary)                                                                                                                                                                                                                   |

|    | Circle one: Carry out? YES NO                                                                                                                                                                                                            |

|    | Circle one: Overflow? YES NO                                                                                                                                                                                                             |

| 4. | (1 point) Let x88 be an 8-bit 2's complement number. What is its decimal value?                                                                                                                                                          |

|    | x88 = (decimal number)                                                                                                                                                                                                                   |

| 5. | (2 points) What is the largest positive number that a 7-bit unsigned number can represent?                                                                                                                                               |

|    | Your answer in decimal:                                                                                                                                                                                                                  |

|    | What is the largest positive number that a 7-bit 2's complement number can represent?                                                                                                                                                    |

|    | Your answer in decimal:                                                                                                                                                                                                                  |

| UIN |  |  |  |  |

|-----|--|--|--|--|

|     |  |  |  |  |

#### Problem 1 (10 points): Binary Representation and Operations

| 1. | (2 points) The current version of Prof. Lumetta's ECE 120 lecture | notes is 170 pages long. If |

|----|-------------------------------------------------------------------|-----------------------------|

|    | Prof. Lumetta decided to refer to each page using fixed-length    | binary words, what is the   |

|    | minimum number of hits needed per page?                           | •                           |

Minimum number of bits: (174)

How many additional pages can Prof. Lumetta add to his lecture notes while keeping the same number of bits?

Additional number of pages: 86 (decimal number) 256-170

- 2. (2 points) Perform the following bitwise logical operations.

- **b.** 1001 XOR ( NOT(0011) ) = \_\_\_\_\_ (binary)

- 3. (3 points) Perform the following operation in 4-bit 2's complement representation.

1010 – 1110 = (binary)

Circle one: Carry out? YES NO

Circle one: Overflow? YES NO

4. (1 point) Let x88 be an 8-bit 2's complement number. What is its decimal value?

x88 = (decimal number)

5. (2 points) What is the largest positive number that a 7-bit unsigned number can represent?

Your answer in decimal: \_\_\_\_127

What is the largest positive number that a 7-bit 2's complement number can represent?

Your answer in decimal: 63

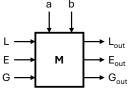

#### Problem 2 (15 points): Bit-Sliced Comparator

In this problem, you will design circuit M (as shown in Figure 1) for a bit-sliced comparator whose bit-slice design is shown in Figure 2. It compares two n-bit unsigned binary numbers  $A = a_{n-1}...a_1a_0$  and  $B = b_{n-1}...b_1b_0$ . It outputs the following.

$$\begin{split} L_{out} &= 1 \text{ if and only if } A < B \\ E_{out} &= 1 \text{ if and only if } A = B \\ G_{out} &= 1 \text{ if and only if } A > B \end{split}$$

Figure 1

Figure 2.

1. (1 point) Specify the initial inputs  $L_n$ ,  $E_n$ , and  $G_n$ .

$$L_n, E_n, G_n =$$

\_\_\_\_\_

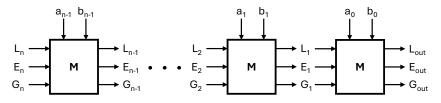

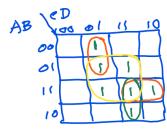

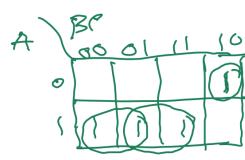

**2. (4 points)** In this and next parts, you will design the circuit M. Give the **minimal SOP** expression for E<sub>out</sub>(a,b,L,E,G). In order to avoid drawing a 5-variable K-map, realize that the expression should not depend on L and G. Therefore, E<sub>out</sub> only depends on the three remaining variables. Use the following 3-variable K-map if needed.

$E_{out}(a,b,L,E,G) =$

| UI |    |  |  |  |

|----|----|--|--|--|

|    | N  |  |  |  |

| v. | 14 |  |  |  |

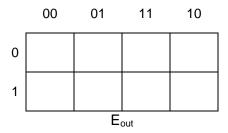

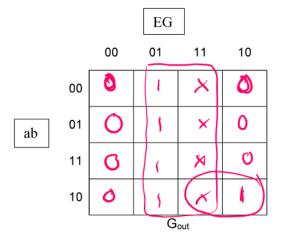

**3. (4 points)** Now give the **minimal SOP** expression for G<sub>out</sub>(a,b,L,E,G). Again, we can avoid a 5-variable K-map by realizing that the expression does not depend on L. Use the following 4-variable K-map if needed. You may use don't-cares in the K-map.

$G_{out}(a,b,L,E,G) =$ \_\_\_\_\_\_

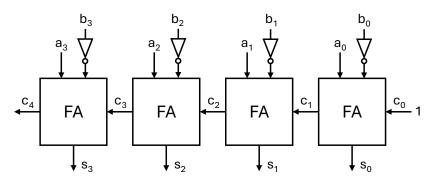

Parts 4, 5, and 6 below are unrelated to Parts 1, 2, and 3 on the previous page. We are now building a 4-bit comparator using the following adder-based circuit.

**4. (2 points)** Although the inputs A and B are unsigned, the above circuit effectively calculates A – B, and the result S can be interpreted as a two's complement number. Based on this knowledge, write down the **Boolean expression for E<sub>out</sub>** which indicates A = B. Write it as a function of adder output signals s<sub>3</sub>, s<sub>2</sub>, s<sub>1</sub>, and s<sub>0</sub>.

| $E_{out} =$ |  |

|-------------|--|

|             |  |

**5.** (2 points) Now write down the Boolean expression for  $L_{out}$  which indicates A < B.  $L_{out}$  can be a function of the adder outputs  $c_4$ ,  $c_3$ ,  $c_2$ ,  $c_1$ ,  $s_3$ ,  $s_2$ ,  $s_1$ , and  $s_0$ .

| $L_{out} =$ |  |  |  |

|-------------|--|--|--|

|             |  |  |  |

|             |  |  |  |

**6. (2 points)** Finally, write down the Boolean expression for  $G_{out}$  which indicates A > B. It can be a function of any adder output signals, or it can be a function of the output signals implemented above, which are  $E_{out}$  and  $L_{out}$ .

| $G_{out} =$ |  |

|-------------|--|

|             |  |

UIN

1. (1 point) Specify the initial inputs  $L_n$ ,  $E_n$ , and  $G_n$ .

2. (4 points) In this and next parts, you will design the circuit M. Give the minimal SOP expression for E<sub>out</sub>(a,b,L,E,G). In order to avoid drawing a 5-variable K-map, realize that the expression should not depend on L and G. Therefore, E<sub>out</sub> only depends on the three remaining variables. Use the following 3-variable K-map if needed.

|                        |   |    |   | 1 _ |

|------------------------|---|----|---|-----|

| $E_{out}(a,b,L,E,G) =$ | ā | ÞE | + | abE |

Expression should be union we

a b

|                  | 00 | 01 | 11 | 10 |  |  |

|------------------|----|----|----|----|--|--|

| 0                | 0  | 0  | 0  | 0  |  |  |

| 1                | ١  | Ø  | -1 | 0  |  |  |

| E <sub>out</sub> |    |    |    |    |  |  |

E = abE + abE

|   |              | bΕ    |       |

|---|--------------|-------|-------|

|   |              | 00 01 | 11 10 |

| Q | Ŏ            |       |       |

|   | (            |       |       |

|   | = \[ \bar{a} | ЪЕ +  | abE   |

|        | a b E | Eoal |

|--------|-------|------|

| 0      | 000   | 0    |

|        | 001   | 1    |

|        | 010   | 0    |

| Z<br>3 | 011   | 0    |

| 4      | 100   | 0    |

| 5      | (01   | 0    |

| 6      | 110   | 0    |

| 7      | 1 ( ) | (    |

| UIN |

|-----|

|-----|

**3. (4 points)** Now give the **minimal SOP** expression for G<sub>out</sub>(a,b,L,E,G). Again, we can avoid a 5-variable K-map by realizing that the expression does not depend on L. Use the following 4-variable K-map if needed. You may use don't-cares in the K-map.

$G_{out}(a,b,L,E,G) = G + \alpha \overline{b} E$

**4. (2 points)** Although the inputs A and B are unsigned, the above circuit effectively calculates A – B, and the result S can be interpreted as a two's complement number. Based on this knowledge, write down the **Boolean expression for E**<sub>out</sub> which indicates A = B. Write it as a function of adder output signals s<sub>3</sub>, s<sub>2</sub>, s<sub>1</sub>, and s<sub>0</sub>.

$E_{out} = \frac{1}{53} \frac{1}{52} \frac{1}{5} \frac{1}{50} \frac{1}{50}$

**5.** (2 points) Now write down the Boolean expression for  $L_{out}$  which indicates A < B.  $L_{out}$  can be a function of the adder outputs  $c_4$ ,  $c_3$ ,  $c_2$ ,  $c_1$ ,  $s_3$ ,  $s_2$ ,  $s_1$ , and  $s_0$ .

L<sub>out</sub> = 53

**6. (2 points)** Finally, write down the Boolean expression for G<sub>out</sub> which indicates A > B. It can be a function of any adder output signals, or it can be a function of the output signals implemented above, which are E<sub>out</sub> and L<sub>out</sub>.

Gout = 53 (52 + 51 + 50)

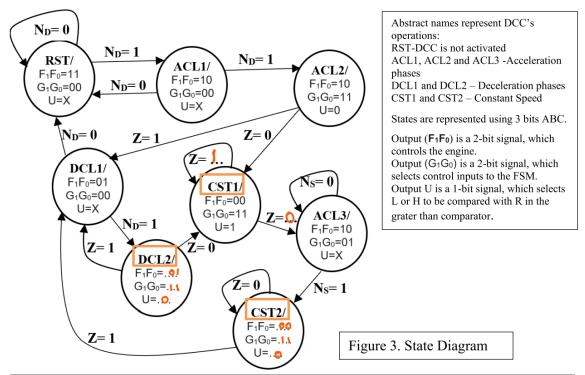

#### Problem 3 (24 points): FSM Design Problem

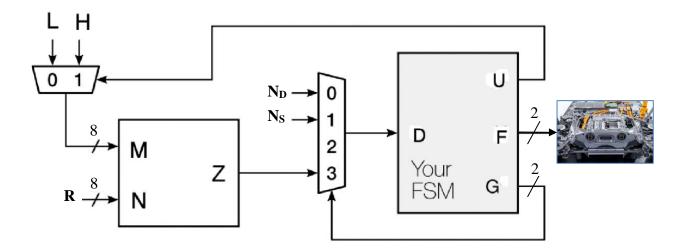

In this problem, you will implement the FSM of a dynamic cruise controller (DCC) used in any modern vehicle. The proposed DCC should automatically adjust your vehicle's speed to maintain a safe distance between your car and the car in front of you. The car uses cameras and other range sensors to measure the distance between the cars on the same lane.

Note: A distance measuring system is already installed in the car and its output R is available to you. R is represented as an 8-bit unsigned value. The DCC is intended to keep your car within a safe distance specified as desired values of L and H, i.e.,  $L \le R < H$ , and L < H.

If R is between L and H, the controller stops accelerating or decelerating the car and instead maintains a constant speed; this is to prevent it from cycling the car decelerating and accelerating too often. For example, to maintain an average distance of 100 feet, L might be 75 feet, and H might be 125 feet.

Note that there is a maximum speed limit. When the car reaches the maximum speed, the car engine would generate a high signal Ns=1. The DCC controller will use the signal to maintain a constant maximum speed until the sensing distance R becomes smaller than L (i.e. R < L). Otherwise, Ns = 0.

Consider another signal  $N_D$ , which is 1 so long as DCC is active, and otherwise 0. Note: for the safety of the system, whenever the driver presses the brake-pedal,  $N_D$  becomes 0.

For some design requirements, your FSM is required to have only a single 1-bit input signal, denoted D (as shown in the following figure). To determine the status of the signals (Ns and  $N_D$ ), they are connected to the multiplexer (whose output is an input to your FSM) that allows you to access the state of the signals as well as the output of the comparator. The circuit is shown in the figure below.

Note that the signal Z is the output of a Greater-Than comparator. Note: Z = 1, if M > N, and 0 otherwise.

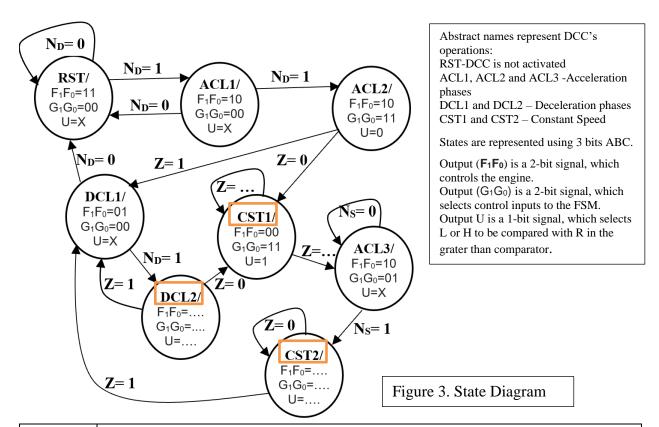

The following state diagram of the Moore FSM of the desired DCC controller is given to you to get started with the implementation of Your FSM. Note: The outputs (U, F, and G) in each state are partially filled with desired bits. The states are described on the table below. The current state of the FSM is denoted as ABC. The input to your FSM is 1-bit signal D. The output of your FSM are three signals F, U and G. Signal U controls the multiplexer that selects the M input to the comparator. Signal F is a 2-bit signal ( $F_1F_0$ ) that controls the engine. We choose the representation as  $F_1F_0 = 00$  (keeps the car at a constant speed),  $F_1F_0=01$  (decelerates the car),  $F_1F_0=10$  (accelerates the car), and  $F_1F_0=11$  (manual mode). G is 2-bit signal ( $G_1G_0$ ) that controls the multiplexer for the input D. U can be don't care (X) if not used in a state.

| States/  | Description                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------|

| ABC      |                                                                                                         |

| RST/000  | Reset state. It keeps the car in manual mode. It checks $N_D$ and makes a transition if $N_D = 1$       |

| ACL1/001 | Acceleration state 1. It accelerates the car. It checks $N_D$ and makes necessary transitions.          |

| ACL2/010 | Acceleration state 2. It keeps accelerating the car. It checks <b>L</b> , compares it with <b>R</b> and |

|          | makes necessary transitions.                                                                            |

| DCL1/011 | Deceleration state 1. It decelerates the car. It checks $N_D$ and makes necessary transitions.          |

| CST1/100 | Constant speed state 1. It keeps the car at a constant speed. It checks <b>H</b> , compares it with     |

|          | R and makes necessary transitions.                                                                      |

| DCL2/101 | Decelerate state 2. It keeps decelerating the car. It checks L, compares it with R and                  |

|          | makes necessary transitions.                                                                            |

| ACL3/110 | Accelerate state 3. It keeps accelerating the car. It checks N <sub>S</sub> and makes necessary         |

|          | transitions.                                                                                            |

| CST2/111 | Constant speed state 2. It keeps the car at a constant speed. It checks L and makes                     |

|          | necessary transitions.                                                                                  |

| UIN | 1 |  |  |  |  |  |  |  |

|-----|---|--|--|--|--|--|--|--|

|     |   |  |  |  |  |  |  |  |

- **1.** [8 points] Fill out the missing information of states DCL2, CST1 and CST2 on the state diagram of figure 3.

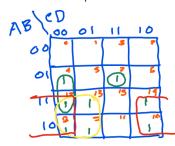

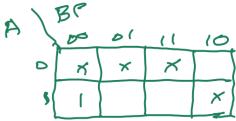

- **2.** [6 points] Draw the next state transition table and derive the next state transition expression in minimal SOP. Let A+,B+,C+ denote the next state of the FSM. Hint: The FSM has only one input D. Thus, you need 4-variable k-map.

|  |  | UIN |

|--|--|-----|

|--|--|-----|

| 3. | [2 points] Derive | the expression | output expression | n F₀ in terms of A | , B, C in minimal SOP |

|----|-------------------|----------------|-------------------|--------------------|-----------------------|

|----|-------------------|----------------|-------------------|--------------------|-----------------------|

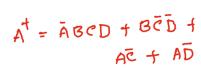

4. [2 points] Derive the expression output expression  $F_1$  in terms of A, B, C in minimal SOP

5. [2 points] Derive the expression U in terms of A, B, C in minimal SOP

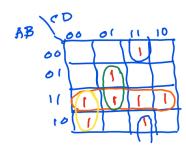

6. [2 point] Derive the expression G<sub>0</sub> in terms of A, B, C in minimal SOP

7. [2 point] Derive the expression  $G_1$  in terms of A, B, C in minimal SOP

| States/  | Description                                                                                                                            |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| ABC      |                                                                                                                                        |

| RST/000  | Reset state. It keeps the car in manual mode. It checks $N_D$ and makes a transition if $N_D = 1$                                      |

| ACL1/001 | Acceleration state 1. It accelerates the car. It checks $N_D$ and makes necessary transitions.                                         |

| ACL2/010 | Acceleration state 2. It keeps accelerating the car. It checks <b>L</b> , compares it with <b>R</b> and makes necessary transitions.   |

| DCL1/011 | Deceleration state 1. It decelerates the car. It checks $N_D$ and makes necessary transitions.                                         |

| CST1/100 | Constant speed state 1. It keeps the car at a constant speed. It checks <b>H</b> , compares it with R and makes necessary transitions. |

| DCL2/101 | Decelerate state 2. It keeps decelerating the car. It checks L, compares it with R and makes necessary transitions.                    |

| ACL3/110 | Accelerate state 3. It keeps accelerating the car. It checks $N_s$ and makes necessary transitions.                                    |

| CST2/111 | Constant speed state 2. It keeps the car at a constant speed. It checks L and makes                                                    |

|          | necessary transitions.                                                                                                                 |

2. [6 points] Draw the next state transition table and derive the next state transition expression in minimal SOP. Let A<sup>+</sup>,B<sup>+</sup>,C<sup>+</sup> denote the next state of the FSM. Hint: The FSM has only one input D. Thus, you need 4-variable k-map.

C512

$$C^{\dagger} = \overline{A} CD + BD + ABC$$

+ ACD

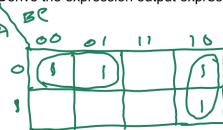

3. [2 points] Derive the expression output expression F<sub>0</sub> in terms of A, B, C in minimal SOP

| ABC  | Fi | Fo  | G, Go | U |

|------|----|-----|-------|---|

| 000  | 1  | 1   | 0 0   | × |

| 001  | s  | 0   | 0 0   | * |

| 010  | (  | O   | 1 5   | O |

| 011  | 0  | 1   | 0 0   | × |

| 100  | 0  | 0   | 5 5   | ٢ |

| 101  | ٥  | £ . | 1 5   | 6 |

| 5 50 | S  | 0   | 0 5   | × |

| 111  | 0  | 0   | 1 1   | ٥ |

| 111  |    |     | 1 1   | 0 |

| UIN |

|-----|

|-----|

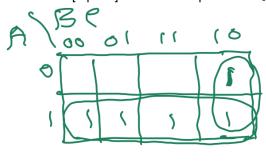

**4.** [2 points] Derive the expression output expression  $F_1$  in terms of A, B, C in minimal SOP

5. [2 points] Derive the expression U in terms of A, B, C in minimal SOP

$$U = \overline{B}\overline{e}$$

$OS$

$$U = A\overline{e}$$

${f 6}.$  [2 point] Derive the expression  $G_0$  in terms of A, B, C in minimal SOP

7. [2 point] Derive the expression  $G_1$  in terms of A, B, C in minimal SOP

8

| U | 11 | ١ |  |

|---|----|---|--|

|   |    |   |  |

## Problem 4 (10 points): LC-3 Interpretation and Assembly

1. The program below consists of LC-3 instructions and data.

| x3000 | 0010 | 0110 | 0000 | 1011 | LD R3, #11     |

|-------|------|------|------|------|----------------|

| x3001 | 0101 | 1011 | 0110 | 0000 |                |

| x3002 | 0110 | 1100 | 1100 | 0000 |                |

| x3003 | 0000 | 0110 | 0000 | 0011 | BRzp #3        |

| x3004 | 1001 | 1001 | 1011 | 1111 |                |

| x3005 | 0001 | 1101 | 0010 | 0001 |                |

| x3006 | 0111 | 1100 | 1100 | 0000 |                |

| x3007 | 0001 | 0110 | 1110 | 0001 |                |

| x3008 | 0001 | 1011 | 0110 | 0001 | ADD R5, R5, #1 |

| x3009 | 0001 | 1101 | 0111 | 1000 |                |

| x300A | 0000 | 1001 | 1111 | 0111 |                |

| x300B | 1111 | 0000 | 0010 | 0101 | HALT           |

| x300C | 1111 | 0000 | 0000 | 0000 | FILL .xF000    |

- a. **(8 points)** Decode the remaining instructions in the program above into LC-3 assembly language using the format shown in those already done for you. Note that all blanks correspond to instructions, not data.

- b. (2 points) In twenty words or less, explain what the program does.

UIN

## 1. The program below consists of LC-3 instructions and data.

x3000 0010 0110 0000 1011 LD R3, #11

x3001 0101 1011 0110 0000 x3002 0110 1100 1100 0000

x3003 0000 0110 0000 0011 BRzp #3

x3004 1001 1001 1011 1111

x3005 0001 1101 0010 0001

x3006 0111 1100 1100 0000 x3007 0001 0110 1110 0001

x3008 0001 1011 0110 0001 ADD R5, R5, #1

x3009 0001 1101 0111 1000

x300A 0000 1001 1111 011<u>1</u>

x300B 1111 0000 0010 0101 HALT

x300C 1111 0000 0000 0000 FILL .xF000

b. (2 points) In twenty words or less, explain what the program does.

8 memory location Starti Read Consecutive from . FOOD. If the value read is negative, invest the value (i.e. make it positive) and put

| U | 11 | ١ |  |  |  |  |  |

|---|----|---|--|--|--|--|--|

|   |    |   |  |  |  |  |  |

#### Problem 5 (24 points)

In this problem we introduce a new instruction to the LC3 instruction set, called STLDR.

STLDR BaseR1, BaseR2, OP2\*

Note: OP2 may be SR2 or SEXT[imm5] IR[5] bit =1 if OP2 is SEXT[imm5], else 0.

This instruction copies a value from one memory location whose address is stored in the register specified by IR[11:9] bits to another memory location whose address is specified as a Baserelative address, **BaseR2+OP2**. STLDR has opcode 1101 and the RTL is:

$$M[BaseR2 + OP2] \leftarrow M[BaseR1]$$

1. (4 points) Give the binary encoding of the instruction **STLDR R3**, **R4**, **R5** by filling in the missing bits.

| Ī | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| - |    |    |    |    |    |    |   |   |   |   | 0 | 0 | 0 |   |   |   |

2. (2 points) Identify the bug in the instruction **STLDR R2, R1, #-32**.

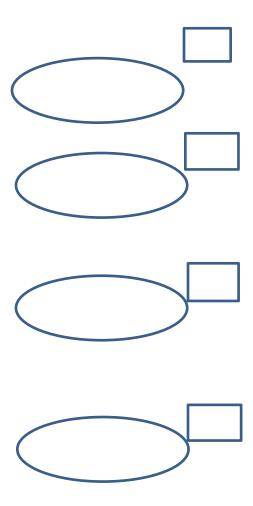

3. (6 points) Fill the missing microinstructions that implement the STLDR instruction **after the decode state**.

Answer: 1.  $MAR \leftarrow BaseR1$

2. \_\_\_\_\_

3.

4. \_\_\_\_\_

4. (4 points) Draw the state diagram for **STLDR** after the decode state with the arc labels as needed, the RTLs mentioned in the states, and include the state numbers in the boxes provided. State numbers 51, 52, 53, and 54 are available as additional states for your use. Hint: your answer should be consistent with the simplified Patt and Patel microsequencer circuit attached to this booklet.

Note:  $51_{10} = 110011_2$ ,  $52_{10} = 110100_2$ ,  $53_{10} = 110101_2$ ,  $54_{10} = 110110_2$

| UIN |  |

|-----|--|

|-----|--|

5. **(8 points)** Determine the control ROM microinstructions that implement the RTL statements from part (3). Complete the table below by filling in **0**, **1**, or **x** as appropriate. Specify ROM addresses in **decimal**. Note that your first state number is implied by the decode strategy used in the LC-3 microarchitecture. State numbers 51, 52, 53, and 54 are available as additional states for your use. The order needs to match your solution in part (3).

|             |        | ROM address in decimal |

|-------------|--------|------------------------|

|             |        | IRD                    |

|             |        | COND(3), COND0 is LSB  |

|             |        | J(6), J0 is the LSB    |

|             | D      | I D REN                |

|             | ) nc   | LDMAR                  |

|             | ıt fi  | LD.MDR                 |

|             | 11 ir  | LD.IR                  |

|             | 1 da   | LD.PC                  |

| -           | tan    | LD.REG                 |

|             | ath    | LC.CC                  |

|             | con    | GateMARMITX            |

|             | trol   | GateMDR                |

|             | 1 11/6 | GateALU                |

|             | ord f  | GatePC                 |

|             | field  | MARMUX                 |

|             | c for  | PCMUX(2)               |

|             | the    | ADDRIMUX               |

|             | co tv  | ADDR2MUX(2)            |

| yo<br>g two | VO.    | DRMUX(2)               |

| ).          |        | SR1MUX(2)              |

|             |        | ALUK(2)                |

|             |        | MIO.EN                 |

|             |        | R.W                    |

UIN

1. (4 points) Give the binary encoding of the instruction STLDR R3, R4, R5 by filling in the missing bits.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 1  | 1  | 0  | 1  | 0  | 1  | ſ | 1 | 0 | 0 | 0 | 0 | 0 | 5 | ۵ | 1 |

2. (2 points) Identify the bug in the instruction STLDR R2, R1, #-32

3. (6 points) Fill the missing microinstructions that implement the STLDR instruction after the decode state.

Answer: 1.  $MAR \leftarrow BaseR1$

| JIN |  |  |  |

|-----|--|--|--|

4. (4 points) Draw the state diagram for **STLDR** after the decode state with the arc labels as needed, the RTLs mentioned in the states, and include the state numbers in the boxes provided. State numbers 51, 52, 53, and 54 are available as additional states for your use. Hint: your answer should be consistent with the simplified Patt and Patel microsequencer circuit attached to this booklet.

Note:  $51_{10} = 110011_2$ ,  $52_{10} = 110100_2$ ,  $53_{10} = 110101_2$ ,  $54_{10} = 110110_2$

| UIN |  |

|-----|--|

|-----|--|

5. **(8 points)** Determine the control ROM microinstructions that implement the RTL statements from part (3). Complete the table below by filling in **0**, **1**, or **x** as appropriate. Specify ROM addresses in **decimal**. Note that your first state number is implied by the decode strategy used in the LC-3 microarchitecture. State numbers 51, 52, 53, and 54 are available as additional states for your use. The order needs to match your solution in part (3).

| ROM address in decimal | IRD | COND(3), COND0 is LSB | J(6), J0 is the LSB | I D DEN | LD.BEIN | LD.MDR | LD.IR | LD.PC | LD.REG | LC.CC | GateMAPMIX | GateMDR | GateALU | GatePC | MARMUX | PCMUX(2) | ADDRIMUX | ADDR2MUX(2) | DRMUX(2) | SR1MUX(2) | ALUK(2) | MIOIM | R.W |

|------------------------|-----|-----------------------|---------------------|---------|---------|--------|-------|-------|--------|-------|------------|---------|---------|--------|--------|----------|----------|-------------|----------|-----------|---------|-------|-----|

| 13                     | 0   | 000                   | 110100              | D       | o no    | ot fi  | 11 ir | n da  | itap   | ath   | cor        | itro    | l wo    | ord    | field  | s for    | the      | se tw       | /O       |           |         |       |     |

| 52                     | 0   | 100                   | 110100              | m       | icro    | oins   | truc  | ctio  | ns.    | Bu    | t be       | su      | re to   | o fil  | l in t | he re    | emai     | ining       | two      |           |         |       |     |

| 54                     | 0   | 000                   | 010000              | Q       | 1       | 0      | 0     | 0     | O      | 0     | 0          | 0       | ſ       | 0      | X      | XX       | ×        | KX          | ×x       | 01        | 00      | 0     | ×   |

| 16                     | 0   | 001                   | 010000              | 6       | 0       | 0      | 0     | 0     | 0      | σ     | 0          | 0       | 0       | 0      | *      | xr       | X        | <b>79</b> < | XX       | **        | XX      | (     | 1   |

| I | 11 | u |  |  |  |

|---|----|---|--|--|--|

|   |    |   |  |  |  |

## Problem 6 (7 points): LC3 Basics

- 1. (1+4 points) Shifting Time:

- a. Suppose a register has a value x0002. What is the value of the register **in hex** after shifting the bits to the **left by 2 bits?**

Answer: x\_\_\_\_\_

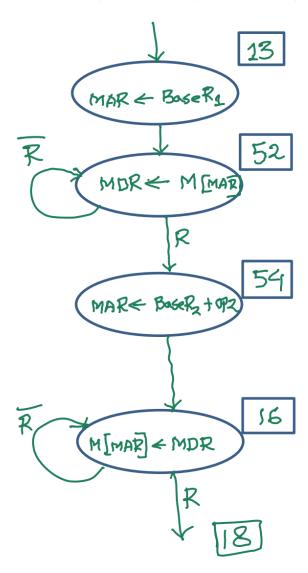

**b.** Complete the following assembly program to shift the value stored in R3 to the left by four bits. Assume there is some initial value in R3.

.ORIG x3000

AND R2,R2,#0

ADD R2,R2,#4

LOOP BRZ DONE

BRnzp LOOP

DONE HALT

.END

2. [2 points] One of our resident ECE programmers intended to write an LC-3 program to output a % to the monitor and then halt. Unfortunately, the programmer got confused about the semantics of each of the opcodes (i.e., exactly what function is carried out by the LC-3 in response to each opcode). Replace exactly one opcode in this program with the correct one to make the program work as intended, mentioning the line number and the corrected instruction as your answer.

.ORIG x3000 ;line 0

STI R0, LABL ;line 1

OUT ;line 2

HALT ;line 3

LABL .STRINGZ "%" ;line 4

.END ;line 5

Answer: Line number:\_\_\_\_\_Correct Instruction:\_\_\_\_\_

#### (5 points) Shifting Time:

a. Suppose a register has a value x0002. What is the value of the register **in hex** after shifting the bits to the **left by 2 bits?**

Answer: x 0008

**b.** Complete the following assembly program to shift the value stored in R3 to the left by four bits. Assume there is some initial value in R3.

2. [2 points] One of our resident ECE programmers intended to write an LC-3 program to output a character % to the monitor and then halt. Unfortunately, the programmer got confused about the functions of the opcodes. Replace exactly one instruction in this program with the correct one to make the program work as intended. Mention the line number and the corrected instruction as your answer.

.ORIG x3000 ;line 0

STI R0, LABL ;line 1

OUT ;line 2

HALT ;line 3

LABL .STRINGZ "%" ;line 4

.END ;line 5

Answer: Line number: 1 Correct Instruction: LD Ro, LABL

## Problem 7 (10 points): LC-3 Assembly Language Interpretation

1. [3 points] In each of the three small programs below, assume that memory location x3004 has been initialized with some bits before the programs are run. We know that the 16 bits in that location may be interpreted as a 2's complement integer, an address, an ASCII value, or an instruction. For each program indicate what the value in x3004 is interpreted as.

```

A)

.ORIG x3000

LDI RO, H

ADD RO, RO, #1

HALT

Η

.FILL x3004

.END

Answer:

B)

.ORIG x3000

LDI RO, J

LDR R1, R0, #0

HALT

J

.FILL x3004

.END

Answer:

C)

.ORIG x3000

LDI RO, K

OUT

HALT

.FILL x3004

K

.END

Answer:

```

2. [4 points] Consider the following LC-3 assembly language program:

```

.ORIG x3000

L1

LEA R1, L1

R2, R2, x0

AND

R2, R2, x2

ADD

R3, P1

LD

LDR RO, R1, xC

L2

OUT

ADD

R3, R3, #-1

BRz

DONE

R1, R1, R2

ADD

BR

L2

```

| U | 11 | 1 |  |  |  |  |  |

|---|----|---|--|--|--|--|--|

|   |    |   |  |  |  |  |  |

```

DONE HALT

P1 .FILL x7

.STRINGZ "NNeaummaasntne!?"

.END

```

A) After this program is assembled and loaded, what binary pattern is stored in memory location x3005?

Answer (Convert the binary pattern into Hex):

B) What is the output of this program?

Answer:

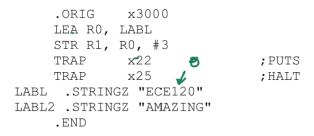

3. [3 points] The following LC-3 program is assembled and then executed. There are no assemble time or run-time errors. Assume all registers are initialized to 0 before the program executes.

A) What is the address of the memory location labeled LABL?

Answer: \_\_\_\_\_

B) What is the address of the memory location labeled LABL2?

Answer: \_\_\_\_\_

C) What is the output of this program?

Answer: \_\_\_\_\_

| UIN  |  |  |  |

|------|--|--|--|

| UIIV |  |  |  |

## Problem 7 (10 points): LC-3 Assembly Language Interpretation

1. [3 points] In each of the three small programs below, assume that memory location x3004 has been initialized with some bits before the programs are run. We know that the 16 bits in that location may be interpreted as a 2's complement integer, an address, an ASCII value, or an instruction. For each program indicate what the value in x3004 is interpreted as.

A)

```

.ORIG x3000

LDI RO, H

ADD RO, RO, #1

HALT

.FILL x3004

.END

```

Η

J

Answer: 25 Complement Integer

B)

Answer: An Address

13

UIN

C)

Answer: An ASell Value

|   | IN  |  |  |  |

|---|-----|--|--|--|

| u | 117 |  |  |  |

2. [4 points] Consider the following LC-3 assembly language program:

```

.ORIG x3000

L1

LEA R1, L1

R2, R2, x0

AND

R2, R2, x2

ADD

LD

R3, P1

L2

LDR RO, R1, xC

OUT

ADD

R3, R3, #-1

BRz

DONE

ADD

R1, R1, R2

BR

L2

DONE HALT

Р1

.FILL x7

.STRINGZ "NNeaummaasntne!?"

.END

```

A) After this program is assembled and loaded, what binary pattern is stored in memory location x3005?

Answer (Convert the binary pattern into Hex): 11 11 6 000 0010 0001 = x F 021

B) What is the output of this program?

Answer: Neumann

3. [3 points] The following LC-3 program is assembled and then executed. There are no assemble time or run-time errors. Assume all registers are initialized to 0 before the program executes.

14

| UIN |  |  |  |

|-----|--|--|--|

|     |  |  |  |

A) What is the address of the memory location labeled LABL?

Answer: × 3004

B) What is the address of the memory location labeled LABL2?

Answer: × 300B

C) What is the output of this program?

Answer: <u>FCF</u>