| U | ΙIΝ |  |

|---|-----|--|

|---|-----|--|

# Fall 2024 – Midterm 2

Tuesday, October 22, 2024

Write your answers only in the space provided. We will not grade the back side of the pages

- Ensure that your exam booklet has 14 pages.

- Please, write your NAME, NetID, and UIN clearly.

- Do not tear the exam booklet apart. You can only detach the last two pages, (ASCII Table and scratch paper) if needed.

- This is a closed book/notes exam. You may use a calculator.

- You are allowed **one handwritten sheet** of notes (both sides). Write your name on the cheat sheet. The cheat sheet will be collected at the end of your exam.

- Absolutely no interaction between students is allowed.

- Clearly indicate any assumptions that you make.

- The questions are not weighted equally. Budget your time accordingly.

- Show your work and write legibly. Solutions in illegible handwriting will be graded as incorrect.

- Write your UIN (9-digit #) on each page in the provided space.

| NAME  | ANSWER    | R KEY      |     |

|-------|-----------|------------|-----|

|       |           |            |     |

| NetID |           |            | UIN |

|       |           |            |     |

|       | Problem 1 | 18 points  |     |

|       | Problem 2 | 27 points  |     |

|       | Problem 3 | 21 points  |     |

|       | Problem 4 | 13 points  |     |

|       | Problem 5 | 21 points  |     |

|       | Total     | 100 points |     |

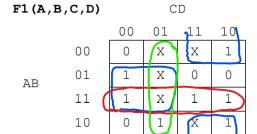

# Problem 1 (18 points): K-maps and CMOS

Consider two 4-variable functions F1 (A,B,C,D) and F2 (A,B,C,D), with the following Kmaps:

Minimal SOP

Minimal POS

| F1 (A, E | 3,C,D) |    | С  | D  |    |

|----------|--------|----|----|----|----|

|          |        | 00 | 01 | 11 | 10 |

|          | 00     | 0  | Х  | X  | 1  |

| AB       | 01     | 1  | Х  | 0  | 0  |

| 112      | 11     | 1  | Х  | 1  | 1  |

|          | 10     | 0  | 1  | Х  | 1  |

F2(A,B,C,D) CD00 01 11 10 00 0 Χ 0 01 0 0 0 X Χ Χ 11 1 1 10 0 1 Χ 0

1. (3 points) Give a minimal SOP expression for F1 (A, B, C, D) and show the corresponding loops on the left map.

Minimal SOP:

$$F1(A,B,C,D) =$$

2. (3 points) Is the solution to part 1 unique?

Circle one: UNIQUE

**NOT UNIQUE**

If not unique, write a different minimal SOP solution (but do not mark the loops):

Minimal SOP:

3. (3 points) Give a minimal POS expression for F2 (A, B, C, D) and show the corresponding loops on the right map.

Minimal POS:

**4. (3 points)** Is the solution to part 3 unique?

Circle one: UNIQUE

**NOT UNIQUE**

If not unique, write a different minimal POS solution (but do not mark the loops):

Minimal POS:

F2(A,B,C,D) =

Minimal SOP

Minimal POS

F2(A,B,C,D) CD 00 01 11 00 0 X 0 0 01 AB 11 X Χ 0 10 X

1. (3 points) Give a minimal SOP expression for F1 (A, B, C, D) and show the corresponding loops on the left map.

Minimal SOP:

2. (3 points) Is the solution to part 1 unique?

Circle one: UNIQUE

If not unique, write a different minimal SOP solution (but do not mark the loops):

3. (3 points) Give a minimal POS expression for F2 (A, B, loops on the right map.

Minimal POS:

$$F2(A,B,C,D) =$$

4. (3 points) Is the solution to part 3 unique?

Circle one:

**NOT UNIQUE**

If not unique, write a different minimal POS solution (but do not mark the loops):

Minimal POS:

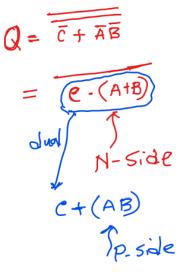

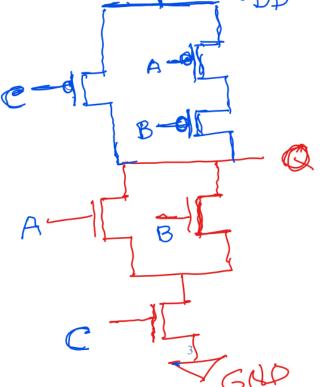

# 5. (6 points) Logic function with CMOS devices

Given the truth table (as shown below) implement the function Q using a single CMOS gate (i.e. the CMOS circuit will have only one gate delay).

hints: write the output  $Q = \overline{(expression)}$ . Then, apply duality principles.

| A | В | С | Output (Q) |

|---|---|---|------------|

| 0 | 0 | 0 | 1          |

| 0 | 0 | 1 | 1          |

| 0 | 1 | 0 | 1          |

| 0 | 1 | 1 | 0          |

| 1 | 0 | 0 | 1          |

| 1 | 0 | 1 | 0          |

| 1 | 1 | 0 | 1          |

| 1 | 1 | 1 | 0          |

#### 5. (6 points) Logic function with CMOS devices

Given the truth table (as shown below) implement the function Q using a single CMOS gate (i.e. the CMOS circuit will have only one gate delay).

hints: write the output  $Q = \overline{(expression)}$ . Then, apply duality principles.

| ABC | 01 11    | 10    |

|-----|----------|-------|

| 00  | 1        |       |

| 1   |          |       |

| Q=  | -<br>で f | (Ā Ē) |

| Α | В | С | Output (Q) |

|---|---|---|------------|

| 0 | 0 | 0 | 1          |

| 0 | 0 | 1 | 1          |

| 0 | 1 | 0 | 1          |

| 0 | 1 | 1 | 0          |

| 1 | 0 | 0 | 1          |

| 1 | 0 | 1 | 0          |

| 1 | 1 | 0 | 1          |

| 1 | 1 | 1 | 0          |

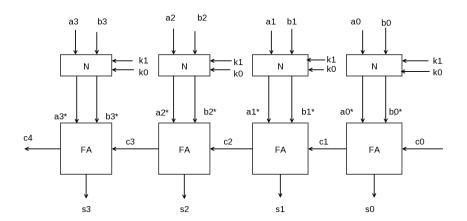

## Problem 2 (27 points): Design of an Arithmetic unit (bit slice design)

Shown below is the structure of an arithmetic unit, consisting of four 1-bit Full Adders (FAs) and four copies of a circuit N:

| <b>K</b> 1 | k <sub>0</sub> | Function    |

|------------|----------------|-------------|

| 0          | 0              | -A PLUS B   |

| 0          | 1              | A PLUS B    |

| 1          | 0              | A MINUS 1   |

| 1          | 1              | -2A MINUS 1 |

Design a 4-bit arithmetic unit that accepts inputs  $a_3$ , ...,  $a_0$ , and  $b_3$ , ...,  $b_0$ , interpreted as the 4-bit two's-complement representations of integers A and B, and control inputs  $k_1$ ,  $k_0$ , and performs the arithmetic operations defined in the above table.

**1. (9 points)** Fill in the following table by expressing values of  $a_i^*$ ,  $b_i^*$ , and  $c_0$  in terms of  $a_i$ ,  $b_i$ , their complements, and constant binary values. The second row is already filled in for you as an example. *Hints:* -A = NOT(A) + 1

| <b>k</b> <sub>1</sub> | k <sub>0</sub> | Operation   | a <sub>i</sub> * | b <sub>i</sub> * | C <sub>0</sub> |

|-----------------------|----------------|-------------|------------------|------------------|----------------|

| 0                     | 0              | -A PLUS B   |                  |                  |                |

| 0                     | 1              | A PLUS B    | a <sub>i</sub>   | b <sub>i</sub>   | 0              |

| 1                     | 0              | A MINUS 1   |                  |                  |                |

| 1                     | 1              | -2A MINUS 1 |                  |                  |                |

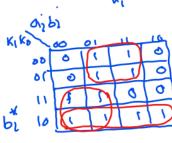

2. (6 points) Express  $a_i^*$  and  $b_i^*$  as functions of  $k_1$ ,  $k_0$ ,  $a_i$ , and  $b_i$ . Write their minimal SOPs: (you may use the provided scratch paper to draw the corresponding K-maps )

| a <sub>i</sub> * | = |  |

|------------------|---|--|

|                  |   |  |

$$b_i^* = \underline{\hspace{1cm}}$$

3. (2 points) Define  $c_0$  as a function of  $k_1$ ,  $k_0$  using a single gate.

$$c_0 =$$

1. (9 points) Fill in the following table by expressing values of  $a_i^*$ ,  $b_i^*$ , and  $c_0$  in terms of  $a_i$ ,  $b_i$ , their complements, and constant binary values. The second row is already filled in for you as an example. *Hints:* -A = NOT(A)+1

| k <sub>1</sub> | k <sub>0</sub> | Operation   | a <sub>i</sub> *      | b <sub>i</sub> * | C <sub>0</sub> |

|----------------|----------------|-------------|-----------------------|------------------|----------------|

| 0              | 0              | -A PLUS B   | $\overline{\alpha}_i$ | bi               | 1              |

| 0              | 1              | A PLUS B    | ai                    | bi               | 0              |

| 1              | 0              | A MINUS 1   | $a_i$                 | 1                | 0              |

| 1              | 1              | -2A MINUS 1 | 0;                    | αį               | 1              |

2. (6 points) Express  $a_i^*$  and  $b_i^*$  as functions of  $k_1$ ,  $k_0$ ,  $a_i$ , and  $b_i$ . Write their minimal SOPs:

(you may use the provided scratch paper to draw the corresponding K-maps) as  $a_{i}^{*} = \frac{\kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i}}{\kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i}}$   $b_{i}^{*} = \frac{\kappa_{i} \alpha_{i} + \kappa_{i} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i}}{\kappa_{i} \kappa_{o} \alpha_{i} + \kappa_{i} \kappa_{o} \alpha_{i}}$

- 3. (2 points) Define  $c_0$  as a function of  $k_1$ ,  $k_0$  using a single gate CO = KI KO + KI KO => KI XNOR KO

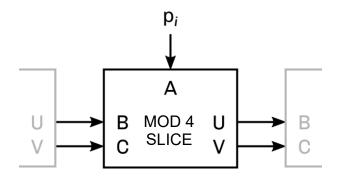

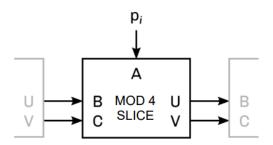

## (2+3+3+1+1 = 10 points) Bit Slice Design - Divisible by 4

**4.** For this problem, you will design a bit-sliced unit to test whether an integer P given in *n*-bit unsigned representation is divisible by 4. Your divisible-by-4 unit should output a two-bit value, denoted UV, with the meaning given by the table below on the right.

Each bit slice takes a bit  $p_i$  of  $P = p_{n-1} \dots p_1 p_0$ , provided as input A to the bit slice, and the two-bit output of the bit slice to the left as inputs B and C. The most significant bit  $p_{n-1}$  is the input to the leftmost bit slice and least significant bit  $p_0$  is the input to the rightmost bit slice.

| UV | Meaning             |

|----|---------------------|

| 00 | P is divisible by 4 |

| 01 | P mod 4 = 1         |

| 10 | P mod 4 = 2         |

| 11 | P mod 4 = 3         |

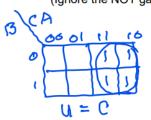

Give a **minimal SOP** expression for the bit slice output variable U, a **minimal POS** expression for the bit slice output variable V, and the initial values for B and C to be provided as the first bit slice's inputs B and C. Note that U and V must be functions of A, B, and C only.

**Hint:** Think about the how the long division process works in the decimal system (and the base-2 system) and how we can use the P mod 4 values to capture the process. Check your bit-sliced circuit with several test values to make sure it produces the expected values of U and V at the least-significant bit position.

a. First bit slice's inputs B and C:

$$B_0 = C_0 =$$

b. A minimal SOP expression for the bit slice output variable U

c. A minimal POS expression for the bit slice output variable V

d. Use the area heuristics to compute the area of each bit-slice:

e. The total gate delay of the n-bit divisible by 4 circuit is: \_\_\_\_\_\_(Ignore the NOT gate delay at the input)

#### (2+3+3+1+1 = 10 points) Bit Slice Design - Divisible by 4

4. For this problem, you will design a bit-sliced unit to test whether an integer P given in n-bit unsigned representation is divisible by 4. Your divisible-by-4 unit should output a two-bit value, denoted UV, with the meaning given by the table below on the right.

Each bit slice takes a bit  $p_i$  of  $P = p_{n-1} \dots p_1 p_0$ , provided as input A to the bit slice, and the two-bit output of the bit slice to the left as inputs B and C. The most significant bit  $p_{n-1}$  is the input to the leftmost bit slice and least significant bit  $p_0$  is the input to the rightmost bit slice.

| UV | Meaning             |

|----|---------------------|

| 00 | P is divisible by 4 |

| 01 | P mod 4 = 1         |

| 10 | P mod 4 = 2         |

| 11 | P mod 4 = 3         |

Q

Give a **minimal SOP** expression for the bit slice output variable U, a **minimal POS** expression for the bit slice output variable V, and the initial values for B and C to be provided as the first bit slice's inputs B and C. Note that U and V must be functions of A, B, and C only.

**Hint:** Think about the how the long division process works in the decimal system (and the base-2 system) and how we can use the P mod 4 values to capture the process. Check your bit-sliced circuit with several test values to make sure it produces the expected values of U and V at the least-significant bit position.

a. First bit slice's inputs B and C:

$B_0 = \bigcirc$   $C_0 = \bigcirc$

b. A  $\boldsymbol{\text{minimal SOP}}$  expression for the bit slice output variable U

c. A minimal POS expression for the bit slice output variable V

v = A

d. Use the area heuristics to compute the area of each bit-slice: \_

e. The total gate delay of the n-bit divisible by 4 circuit is:

(Ignore the NOT gate delay at the input)

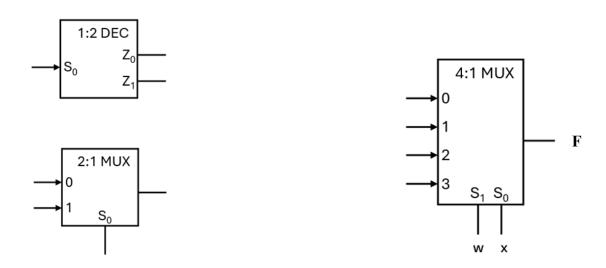

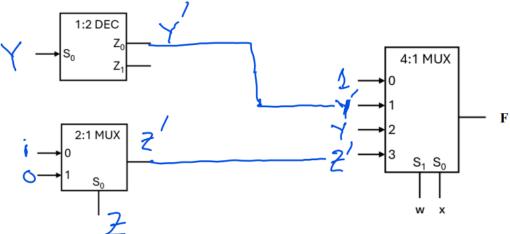

## Problem 3 (21 points): Multiplexers (MUX) and Decoders (DEC)

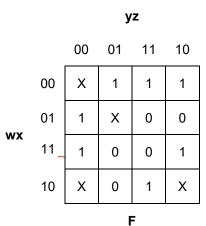

You will implement the circuit for the Boolean function F shown in Part 3. Parts 1 and 2 will help you build the circuit.

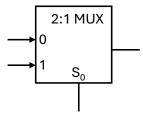

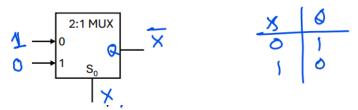

1) (2 points) Implement an inverter using the 2:1 MUX shown below. Label all inputs of the MUX. You are free to use 0's and 1's as inputs. Note: Complemented input is not available.

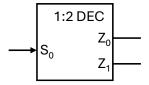

2) (2 points) Now implement an inverter for input y using the 1:2 DEC shown below. Label the input and only one output as **OUT**. You do not need to label both outputs. Complemented input (y') is not available.

Hint: You may fill out the truth table (shown on the right) for the 1:2 DEC with 0's and 1's. The table is only there to help you, and it will **not** be graded.

| Input          | Ou    | tput  |

|----------------|-------|-------|

| S <sub>0</sub> | $Z_0$ | $Z_1$ |

| 0              |       |       |

| 1              |       |       |

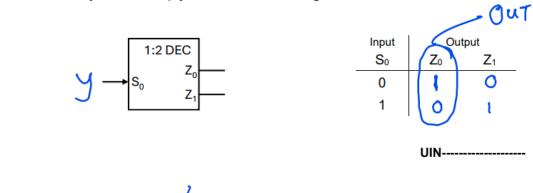

3) (5 points) Based on your answers to Parts 1 & 2, implement F (whose K-map is shown below) using only one 2:1 MUX, one 1:2 DEC, and one 4:1 MUX. The select bits for the 4:1 MUX are fixed as shown below. You may not use any additional gates. Complemented inputs are not available. You do not need to draw any loops on the K-map.

Hints: Look at the K-map, the function values at each row position and their relationship with yz. You are free to assign 0 or 1 to X (don't-care) and you are allowed to use 0's and 1's as inputs to the MUX. Necessary components (Decoder and MUXs) are provided on the next page. Complete the circuit. Note: You may not use any additional gates. Complemented inputs are not available.

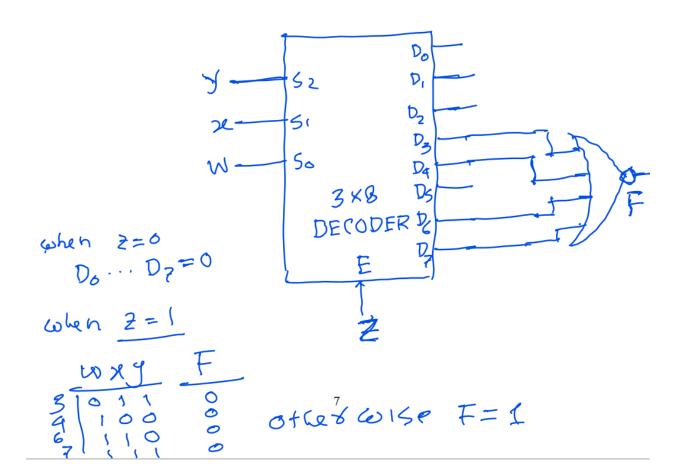

**4) (8 points)** Implement the function F of part 3 using a 3x8 Decoder and a four-input NOR gate. Consider that all the don't cares are 1. Draw the decoder and label its input, outputs, Enable (E), and NOR gates inputs/output clearly (use the space below).

#### Problem 3 (21 points): Multiplexers (MUX) and Decoders (DEC)

You will implement the circuit for the Boolean function F shown in Part 3. Parts 1 and 2 will help you build the circuit.

1) (2 points) Implement an inverter using the 2:1 MUX shown below. Label all inputs of the MUX. You are free to use 0's and 1's as inputs. Note: Complemented input is not available.

2) (2 points) Now implement an inverter for input y using the 1:2 DEC shown below. Label the input and only one output as OUT. You do not need to label both outputs. Complemented input (y') is not available.

Hint: You may fill out the truth table (shown on the right) for the 1:2 DEC with 0's and 1's. The table is only there to help you, and it will **not** be graded.

4) (8 points) Implement the function F of part 3 using a 3x8 Decoder and a four-input NOR gate. Consider that all the don't cares are 1. Draw the decoder and label its input, outputs, Enable (E), and NOR gates inputs/output clearly (use the space below).

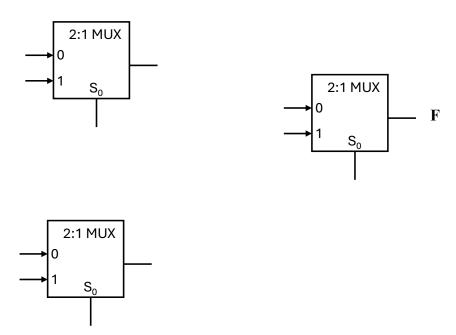

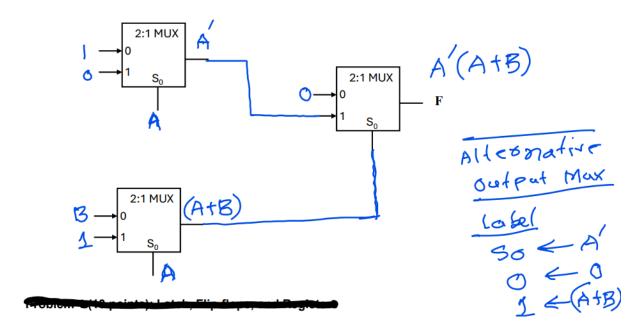

5) (4 points) Implement the following Boolean function F = A'(A+B) using three 2-to-1 MUX (given below). Note: You are free to use 0's and 1's as inputs. DO NOT simplify the expression. You may not use any other logic gates. Assume the Complemented input A' is not available. Hints: how do you implement OR and AND gates using MUX?

5) (4 points) Implement the following Boolean function F = A'(A+B) using three 2-to-1 MUX (given below). Note: You are free to use 0's and 1's as inputs. DO NOT simplify the expression. You may not use any other logic gates. Assume the Complemented input A' is not available. Hints: how do you implement OR and AND gates using MUX?

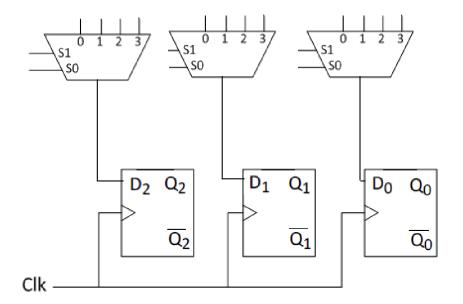

# Problem 4 (13 points): Latch, Flip-flops, and Registers

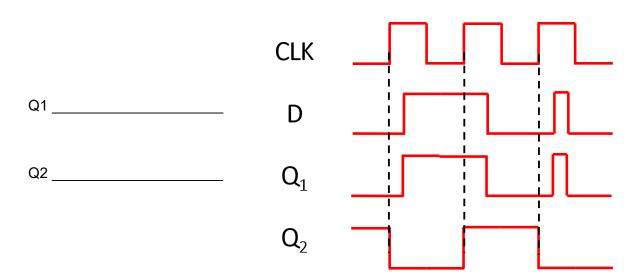

1. (2 points) One of your colleagues designed two sequential circuit elements but forgot which one is a Latch and which one is a flip flop. Based on the timing diagram, please tell him which is a flip-flop and which is a latch?

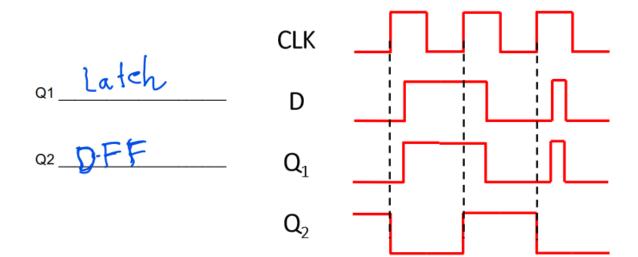

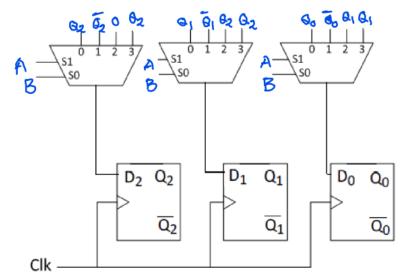

# 2. (11 points) Registers

Consider a 3-bit shift register that has the functionality specified in the table to the right.

(6 points) In the figure below, label the inputs to the muxes to complete the design of this 3-bit register that performs the operations listed in the table. Use labels and do not draw any additional gates or wires.

| Α | В | Operation              |

|---|---|------------------------|

| 0 | 0 | Hold value             |

| 0 | 1 | Bitwise complement     |

| 1 | 0 | Logical shift right    |

| 1 | 1 | Arithmetic shift right |

2. (2 points) If the shift register initially stores  $Q_2Q_1Q_0$ =101, what is stored in the register after one clock cycle when AB=11?

Answer:  $Q_2Q_1Q_0 =$ \_\_\_\_\_

3. (3 points) If the shift register initially stores  $Q_2Q_1Q_0$ =100, and in the next clock cycle, if we want the register to hold the values  $Q_2Q_1Q_0$ =010, what should be A and B and the operation to yield this result?

A = \_\_\_\_\_, B = \_\_\_\_\_, Operation = \_\_\_\_\_

1. (2 points) One of your colleagues designed two sequential circuit elements but forgot which one is a Latch and which one is a flip flop. Based on the timing diagram, please tell him which is a flip-flop and which is a latch?

#### 2. (11 points) Registers

Consider a 3-bit shift register that has the functionality specified in the table to the right.

(6 points) In the figure below, label the inputs to the muxes to complete the design of this 3-bit register that performs the operations listed in the table. Use labels and do not draw any additional gates or wires.

| Α | В | Operation              |

|---|---|------------------------|

| 0 | 0 | Hold value             |

| 0 | 1 | Bitwise complement     |

| 1 | 0 | Logical shift right    |

| 1 | 1 | Arithmetic shift right |

2. (2 points) If the shift register initially stores  $Q_2Q_1Q_0$ =101, what is stored in the register after one clock cycle when AB=11?

Answer:  $Q_2Q_1Q_0 = \frac{1}{2} \sqrt{\frac{1}{2}}$

3. (3 points) If the shift register initially stores  $Q_2Q_1Q_0$ =100, and in the next clock cycle, if we want the register to hold the values  $Q_2Q_1Q_0$ =010, what should be A and B and the operation to yield this result?

A = 1, B = 0, Operation = logical Shift Right

#### Problem 5 (21 points): Design with Components and Abstraction

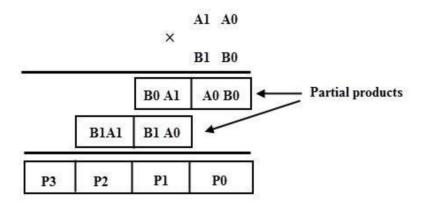

In this problem, you will design binary multipliers that multiply unsigned binary numbers. You will start by examining the multiplication of 2-bit numbers, extend the concepts to 4-bit numbers, and finally generalize the design for multiplying any M-bit and N-bit binary numbers.

#### **Background: Binary Multiplication**

Binary multiplication operates under the same principles as decimal multiplication but uses only two digits: 0 and 1. The fundamental rules for binary multiplication are:

- 0×0=0

- 0×1=0

- 1×0=0

- 1×1=1

When multiplying two binary numbers, each bit of the multiplier is multiplied by each bit of the multiplicand, generating partial products. These partial products are then appropriately shifted (based on their positional value) and summed to produce the final product.

Part 1: (2+10 = 12 points) Understanding 2-bit Binary Multiplication

1.1 Let  $A=A_1A_0$  and  $B=B_1B_0$  be two 2-bit unsigned binary numbers, where  $A_1$  and  $B_1$  are the most significant bits (MSBs), and  $A_0$  and  $B_0$  are the least significant bits (LSBs). Using AND, and ADD operators, write the expressions for each bit  $P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$  of the product  $P=P_3P_2P_1P_0$  resulting from the multiplication of A and B. Note: Carry from  $P_1$  will be denoted as  $C_{in, P1}$ , Carry from  $P_2$  will be denoted as  $C_{in, P2}$

| $P_0 =$          |  |

|------------------|--|

| P <sub>1</sub> = |  |

| P <sub>2</sub> = |  |

| P <sub>3</sub> = |  |

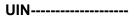

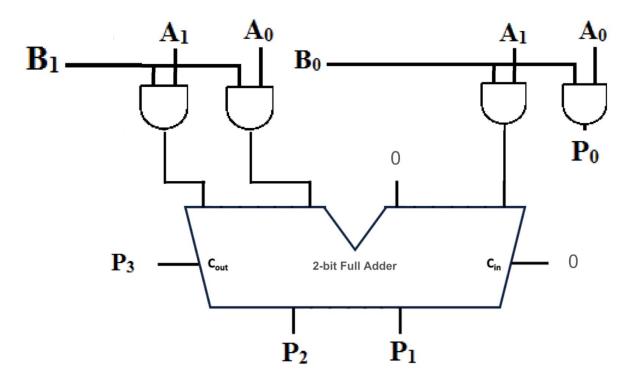

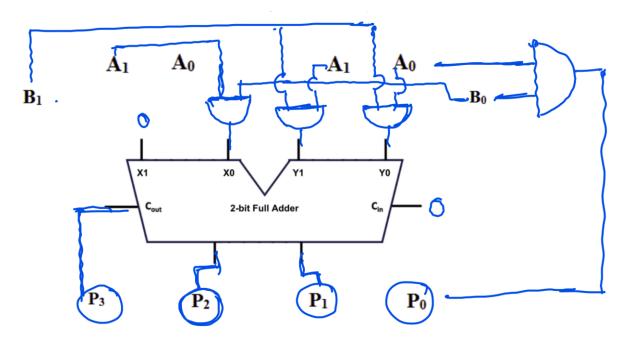

1.2 Complete the following logic schematic diagram of a 2-bit by 2-bit binary multiplier using:

- AND gates to generate the partial products.

- 2-bit Full Adder to sum the partial products.

Ensure that all inputs, outputs, and intermediate signals are clearly labeled.

Part 2 (1+6=7 points): Extending to 4-bit Binary Multiplication

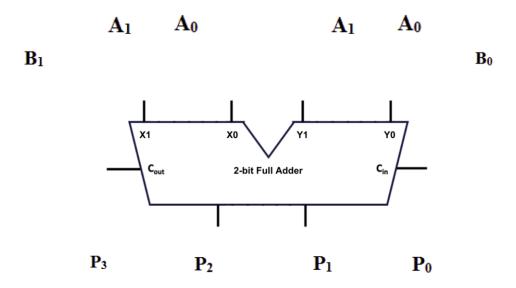

(1 point) Now consider multiplying two 4-bit unsigned binary numbers: begin by analyzing the multiplication process and completing the following diagram for 4-bit by 4-bit binary multiplication (fill in all the partial products generated 4-bit by 4-bit binary multiplication (fill in all the partial products generated when multiplying (4-bit unsigned) A by B)

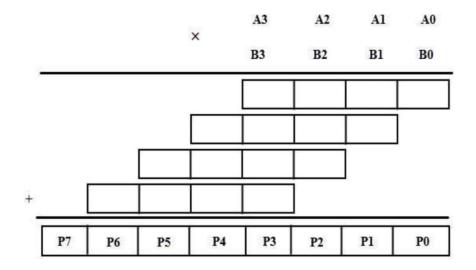

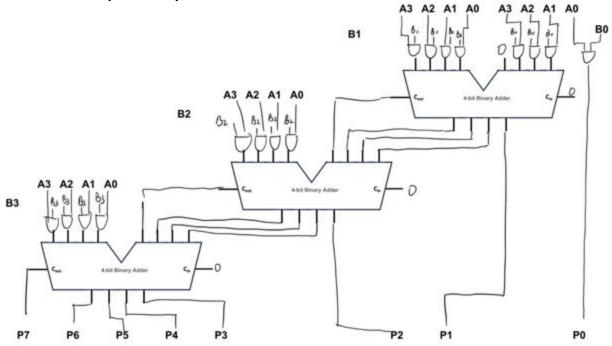

#### (6 points) Designing the Logic Schematic for a 4-bit Binary Multiplication

2.1. Using the concepts from Parts 1 and 2, design a logic schematic diagram for a 4-bit by 4-bit binary multiplier. Your design should use AND gates to generate the partial products and 4-bit binary adders to sum them. (Inputs including:  $A_0 A_1 A_2 A_3 B_0 B_1 B_2 B_3$ ; outputs including:  $P_0 P_1 P_2 P_3 P_4 P_5 P_6 P_7$ )

#### Part 3: (2 pts) Generalizing to M-bit by N-bit Binary Multiplication

Consider multiplying an M-bit unsigned binary number (multiplicand) by an N-bit unsigned binary number (multiplier).

3.1 Determine the number of AND gates required to generate all the partial products for an M-bit by N-bit binary multiplication.

| A nower |  |  |

|---------|--|--|

| Answer: |  |  |

3.2 After generating the partial products, calculate the number of N-bit binary adders needed to obtain the final output?

| Answer: |  |

|---------|--|

|---------|--|

5.1

•

$$P_0 = A_0 B_0$$

•

$$P_1 = (A_1B_0) + (A_0B_1)$$

$$ullet \ P_2 = (A_1 B_1) + C_{{

m in},P_1}$$

$$\bullet$$

$P_3=C_{\mathrm{in},P_2}$

**5.2**

5.2.1

|    |            |      |                               | ×    | A3   | A2    | A1   | A0   |

|----|------------|------|-------------------------------|------|------|-------|------|------|

|    |            |      |                               | ^    | В3   | B2    | B1   | В0   |

|    |            |      |                               |      | BoA3 | BoA2  | BoAI | AoBo |

|    |            |      |                               | A3B1 | AZBI | As By | AoBi |      |

|    |            |      | A <sub>3</sub> B <sub>2</sub> | AZB2 | A1B2 | ABBZ  |      |      |

| +_ |            | A3B3 | AZB3                          | AIB3 | AB3  |       |      |      |

|    | <b>P</b> 7 | P6   | P5                            | P4   | Р3   | P2    | Pl   | P0   |

**Part -2: 5.2 (Circuit)**

5.3.1

# **Need N\*M AND Gates**

5.3.2

Expression dependent on M, not N

# Boolean algebra properties

| Commutativity   | $x \cdot y = y \cdot x$                         | x + y = y + x                           |

|-----------------|-------------------------------------------------|-----------------------------------------|

| Associativity   | $(x \cdot y) \cdot z = x \cdot (y \cdot z)$     | (x + y) + z = x + (y + z)               |

| Distributivity  | $x \cdot (y + z) = x \cdot y + x \cdot z$       | $x + y \cdot z = (x + y) \cdot (x + z)$ |

| Idempotence     | $x \cdot x = x$                                 | x + x = x                               |

| Identity        | $x \cdot 1 = x$                                 | x + 0 = x                               |

| Null            | $x \cdot 0 = 0$                                 | x + 1 = 1                               |

| Complementarity | $x \cdot x' = 0$                                | x + x' = 1                              |

| Involution      |                                                 | (x')' = x                               |

| DeMorgan's      | $(x \cdot y)' = x' + y'$                        | $(x + y)' = x' \cdot y'$                |

| Absorption      | $x \cdot (x + y) = x$                           | $x + x \cdot y = x$                     |

| No-Name         | $x \cdot (x' + y) = x \cdot y$                  | $x + x' \cdot y = x + y$                |

| Consensus       | $(x+y)\cdot(y+z)\cdot(x'+z) = (x+y)\cdot(x'+z)$ | $x \cdot y + y \cdot z + x' \cdot z =$  |

|                 |                                                 | $x \cdot y + x' \cdot z$                |

#### Table of ASCII Characters

| Char I | Dec | Hex | ı | Char | Dec | Hex | ı | Char | Dec | Hex | Char  | Dec | Hex |

|--------|-----|-----|---|------|-----|-----|---|------|-----|-----|-------|-----|-----|

| (nul)  | 0   | 00  | i | (sp) | 32  | 20  | İ | @    | 64  | 40  |       | 96  | 60  |

| (soh)  | 1   | 01  |   | !    | 33  | 21  |   | A    | 65  | 41  | a     | 97  | 61  |

| (stx)  | 2   | 02  |   | **   | 34  | 22  |   | В    | 66  | 42  | l b   | 98  | 62  |

| (etx)  | 3   | 03  |   | #    | 35  | 23  |   | С    | 67  | 43  | C     | 99  | 63  |

| (eot)  | 4   | 04  |   | \$   | 36  | 24  |   | D    | 68  | 44  | d     | 100 | 64  |

| (enq)  | 5   | 05  |   | 용    | 37  | 25  |   | E    | 69  | 45  | e     | 101 | 65  |

| (ack)  | 6   | 06  |   | &    | 38  | 26  |   | F    | 70  | 46  | f     | 102 | 66  |

| (bel)  | 7   | 07  |   | •    | 39  | 27  |   | G    | 71  | 47  | l g   | 103 | 67  |

| (bs)   | 8   | 8 0 |   | (    | 40  | 28  |   | Н    | 72  | 48  | h     | 104 | 68  |

| (ht)   | 9   | 09  |   | )    | 41  | 29  |   | I    | 73  | 49  | i     | 105 | 69  |

| (lf)   | 10  | 0a  |   | *    | 42  | 2a  |   | J    | 74  | 4a  | Ιj    | 106 | 6a  |

| (vt)   | 11  | 0b  |   | +    | 43  | 2b  |   | K    | 75  | 4b  | k     | 107 | 6b  |

| (ff)   | 12  | 0c  |   | ,    | 44  | 2c  |   | L    | 76  | 4c  | 1     | 108 | 6c  |

| (cr)   | 13  | 0d  |   | -    | 45  | 2d  |   | M    | 77  | 4d  | m     | 109 | 6d  |

| (so)   | 14  | 0e  |   |      | 46  | 2e  |   | N    | 78  | 4e  | l n   | 110 | 6e  |

| (si)   | 15  | 0f  |   | /    | 47  | 2f  |   | 0    | 79  | 4 f | 0     | 111 | 6f  |

| (dle)  | 16  | 10  |   | 0    | 48  | 30  |   | P    | 80  | 50  | p     | 112 | 70  |

| (dc1)  | 17  | 11  |   | 1    | 49  | 31  |   | Q    | 81  | 51  | q     | 113 | 71  |

| (dc2)  | 18  | 12  |   | 2    | 50  | 32  |   | R    | 82  | 52  | r     | 114 | 72  |

| (dc3)  | 19  | 13  |   | 3    | 51  | 33  |   | S    | 83  | 53  | s     | 115 | 73  |

| (dc4)  | 20  | 14  |   | 4    | 52  | 34  |   | T    | 84  | 54  | t     | 116 | 74  |

| (nak)  | 21  | 15  |   | 5    | 53  | 35  |   | U    | 85  | 55  | l u   | 117 | 75  |

| (syn)  | 22  | 16  |   | 6    | 54  | 36  |   | V    | 86  | 56  | v     | 118 | 76  |

| (etb)  | 23  | 17  |   | 7    | 55  | 37  |   | M    | 87  | 57  | W     | 119 | 77  |

| (can)  | 24  | 18  |   | 8    | 56  | 38  |   | Χ    | 88  | 58  | X     | 120 | 78  |

| (em)   | 25  | 19  |   | 9    | 57  | 39  |   | Y    | 89  | 59  | У     | 121 | 79  |

| (sub)  | 26  | 1a  |   | :    | 58  | 3a  |   | Z    | 90  | 5a  | z     | 122 | 7a  |

| (esc)  | 27  | 1b  |   | ;    | 59  | 3b  |   | [    | 91  | 5b  | {     | 123 | 7b  |

| (fs)   | 28  | 1c  |   | <    | 60  | 3с  |   | \    | 92  | 5с  |       | 124 | 7c  |

| (gs)   | 29  | 1d  |   | =    | 61  | 3d  |   | ]    | 93  | 5d  | }     | 125 | 7d  |

| (rs)   | 30  | 1e  |   | >    | 62  | 3e  |   | ^    | 94  | 5e  | ~     | 126 | 7e  |

| (us)   | 31  | 1f  |   | ?    | 63  | 3f  |   | _    | 95  | 5f  | (del) | 127 | 7f  |

| UIN |

|-----|

|-----|

# **Scratch Paper**