UIN-----

# **ECE 120: Introduction to Computing**

- Ensure that your exam booklet has 15 pages.

- Please, write your NAME, NetID, and UIN clearly.

- Do not tear the exam booklet apart. You can only detach the last two pages, (ASCII Table and scratch paper) if needed.

- This is a closed book/notes exam. You may use a calculator.

- You are allowed **one handwritten sheet** of notes (both sides). Write your name on the cheat sheet. The cheat sheet will be collected at the end of your exam.

- Absolutely no interaction between students is allowed.

- Clearly indicate any assumptions that you make.

- The questions are not weighted equally. Budget your time accordingly.

- Show your work and write legibly. Solutions in illegible handwriting will be graded as incorrect.

- Write your UIN (9-digit #) on each page in the provided space.

| NAME  |           |            |     |

|-------|-----------|------------|-----|

|       |           |            |     |

| NetID |           |            | UIN |

|       |           |            |     |

|       | Problem 1 | 20 points  |     |

|       | Problem 2 | 20 points  |     |

|       | Problem 3 | 25 points  | ·   |

|       | Problem 4 | 14 points  |     |

|       | Problem 5 | 21 points  |     |

|       | Total     | 100 points |     |

## Problem 1 (16+4 = 20 points): Serialization

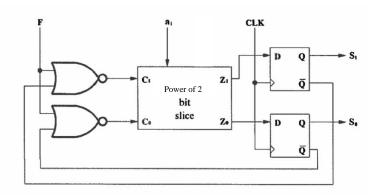

Shown below is a serialized implementation of a power-of-2 checker that checks whether an unsigned integer  $A=a_{\text{N}}-1$   $a_{\text{N}}-2$ .. $a_{\text{N}}=a_{\text{N}}-1$   $a_{\text{N}}=a_{\text{N}$

| $S_1S_0$ | Meaning                       |

|----------|-------------------------------|

| 0 0      | Have not seen any 1s so far   |

| 0 1      | Seen only one '1' so far      |

| 1 0      | Seen more than one '1' so far |

| 11       | Unused                        |

Interpret this circuit as a finite-state machine and complete the following state-transition table.

| S <sub>1</sub> | S <sub>0</sub> | F | a <sub>i</sub> | S <sub>1</sub> + | S <sub>0</sub> + |

|----------------|----------------|---|----------------|------------------|------------------|

| 0              | 0              | 0 | 0              |                  |                  |

| 0              | 0              | 0 | 1              |                  |                  |

| 0              | 0              | 1 | 0              |                  |                  |

| 0              | 0              | 1 | 1              |                  |                  |

| 0              | 1              | 0 | 0              |                  |                  |

| 0              | 1              | 0 | 1              |                  |                  |

| 0              | 1              | 1 | 0              |                  |                  |

| 0              | 1              | 1 | 1              |                  |                  |

| 1              | 0              | 0 | 0              |                  |                  |

| 1              | 0              | 0 | 1              |                  |                  |

| 1              | 0              | 1 | 0              |                  |                  |

| 1              | 0              | 1 | 1              |                  |                  |

| 1              | 1              | 0 | 0              |                  |                  |

| 1              | 1              | 0 | 1              |                  |                  |

| 1              | 1              | 1 | 0              |                  |                  |

| 1              | 1              | 1 | 1              |                  |                  |

**Write down** the  $S_1$ + and  $S_0$ + expressions below:

### Problem 2 (20 points): Sequence Recognizer

In this question, you are going to work with a sequence different from the familiar 0-1 sequence. Your goal is to recognize the pattern "ece" from a random input sequence made up of "e","c" and "b" (Note: Only these three letters will show up).

An example for the FSM is shown below.

Input:

$$\mathbf{X} = \mathbf{e}$$

c e c e e c e b e . . Output:  $\mathbf{R} = 0 \ 0 \ 1 \ 0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 0$

Note: Overlapping instances are counted as shown in the example. The output sequence is delayed by 1 clock cycle

compared to the input sequence because the output **R** is a function of the flip-flop outputs (i.e. the state variables) in a Moore machine. That's why the output sequence becomes 1 in the cycle after "ece" has been recognized by the input.

1. **(3 points)** The first thing you need to do is to define the states for your FSM. We will assume that the FSM starts in state  $S_1S_0=00$ , and each state has the output R indicating if the pattern "ece" has been found (1 for found and 0 for not found). We will also use "x" (representing letters) to label the transitions between the states.

| States (S <sub>1</sub> S <sub>0</sub> ) | Output (R) | State Meanings |

|-----------------------------------------|------------|----------------|

| 00                                      | 0          | Starting state |

| 01                                      |            |                |

| 10                                      |            |                |

| 11                                      |            |                |

2. **(12 points)** Next, fill the state transition table.

(Note:  $S_1$  and  $S_0$  represent the current state and  $S_1^+$  and  $S_0^+$  represent the next state)

| S₁⁺ | S <sub>0</sub> ⁺ | b | С | е | S <sub>1</sub> | S <sub>0</sub> |

|-----|------------------|---|---|---|----------------|----------------|

|     |                  | 1 | 0 | 0 | 0              | 0              |

|     |                  | 0 | 1 | 0 | 0              | 0              |

|     |                  | 0 | 0 | 1 | 0              | 0              |

|     |                  | 1 | 0 | 0 | 0              | 1              |

|     |                  | 0 | 1 | 0 | 0              | 1              |

|     |                  | 0 | 0 | 1 | 0              | 1              |

|     |                  | 1 | 0 | 0 | 1              | 0              |

|     |                  | 0 | 1 | 0 | 1              | 0              |

|     |                  | 0 | 0 | 1 | 1              | 0              |

|     |                  | 1 | 0 | 0 | 1              | 1              |

|     |                  | 0 | 1 | 0 | 1              | 1              |

|     |                  | 0 | 0 | 1 | 1              | 1              |

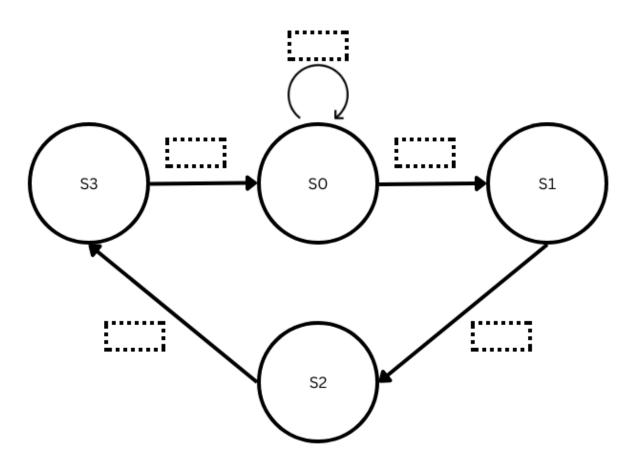

- **3. (5 points)** Finally, it is time to draw your FSM design! While we have prepared a version for you, it only shows some of the transitions and the labels for those transitions are missing. Therefore, your task is to

- (1) Write the missing labels of the given transitions and, (2) complete the missing transitions. Also, for different values of "x" for the same transition, you should write them together on a single arrow like: x1, x2 , where x1 and x2 are different letters.

### Problem 3 (25 points) FSM Design

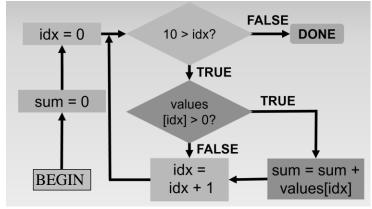

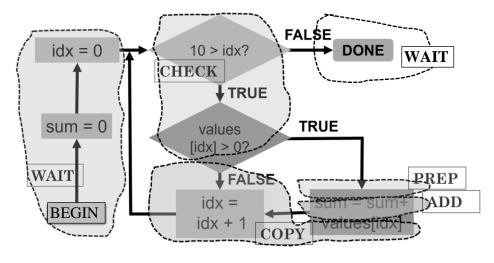

**Problem statement:** Given your knowledge of ECE120, you have been hired as a hardware engineer in a very lucrative company. Your first assignment is to design an FSM to implement the following C code fragment that calculates the sum of a set of 10 integers (stored in an array defined as values[]).

```

int values[10];

int idx;

int sum = 0;

for (idx = 0; 10 > idx; idx = idx + 1)

{

if (values[idx] > 0) {

sum = sum + values[idx];

}

}

```

Figure 1 flow chart of the given C code

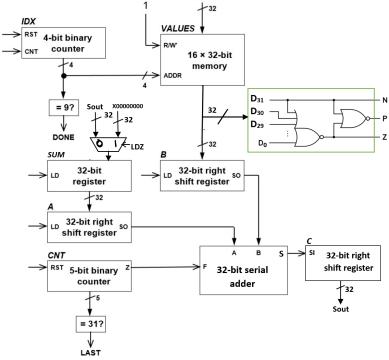

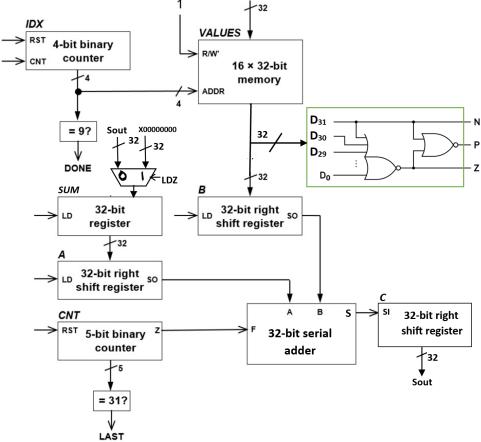

Given the available components, your project teammates have already selected a datapath (as shown in Fig. 2). A brief description of each element in the datapath is given on the last page as an appendix. Note that the datapath uses a 32-bit serial adder to add two integer values, during the calculation of "sum = sum + values[idx]". Your goal is to design the FSM controller that generates the necessary control signals for the datapath to produce the expected functionality.

Figure 2 Datapath

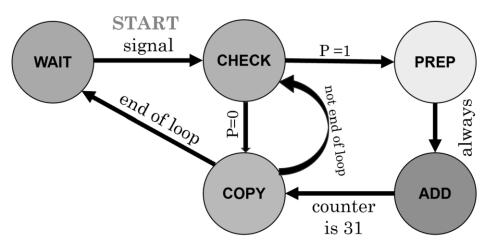

Given the datapath and the flow chart, the first step of the FSM controller design process is to convert the flow chart of the program into its state diagram that can be realizable by the chosen datapath. Your teammates have gone back and forth between the components and the FSM, grouping the flowchart boxes as shown in Fig. 3(a) yielding the state diagram of the desired FSM controller as shown in 3(b).

Figure 3(a)

Figure 3 (b) Desired State Diagram

To help you get started with the design process, you have been given with a partially completed next state transition table (**Fig 4**) along with the RTL of each state, and the partially completed table with the necessary control signals that the state machine needs to generate in every state (**Fig 5**). An external device generates START signal (not shown here) to let the FSM know that the memory has been filled in with 10 integer values

Question: [9+8=17 points] Complete the tables and write expressions (i.e. next states and output expressions) to design the FSM-controller.

| Next state transitions expressions:        | State<br>(S <sub>4</sub> S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> ) | actions (simultaneous)                                                                                 | condition       | next state   |

|--------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|--------------|

| Example:<br>$S_1^+ = S_0.START + S_4.DONE$ | WAIT<br>(00001)                                                                        | IDX ← 0<br>SUM ← X00000000                                                                             | START<br>START' | CHECK        |

|                                            | CHECK<br>(00010)                                                                       | No need to generate any control signal for Datapath. FSM just checks the P signal.                     |                 | PREP<br>COPY |

|                                            | PREP<br>(00100)                                                                        | $A \leftarrow SUM$<br>$B \leftarrow VALUES[IDX]$<br>$CNT \leftarrow 0$                                 | (always)        |              |

|                                            | ADD<br>(01000)                                                                         | Run serial Adder. No need to generate any control signal for Datapath. FSM just checks the LAST signal | LAST            | COPY         |

|                                            | COPY<br>(10000)                                                                        | P: SUM ← Sout IDX ← IDX+1 FSM just checks the DONE signal                                              | DONE'           | WAIT         |

Figure 4

| Output expressions:<br>Example, $IDX.RST = S_0$ | state | S <sub>4</sub> S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | IDX.<br>RST | IDX.<br>CNT | SUM.<br>LD | LDZ | A.<br>LD | B.<br>LD | CNT.RST |

|-------------------------------------------------|-------|----------------------------------------------------------------------------|-------------|-------------|------------|-----|----------|----------|---------|

|                                                 | WAIT  | 00001                                                                      | 1           | 0           | 1          | 1   | 0        | 0        | 0       |

|                                                 | СНЕСК | 00010                                                                      | 0           |             |            |     |          |          |         |

|                                                 | PREP  | 00100                                                                      | 0           |             |            |     |          |          |         |

|                                                 | ADD   | 01000                                                                      | 0           |             |            |     |          |          |         |

|                                                 | СОРУ  | 10000                                                                      | 0           | 1           | P          | 0   |          |          |         |

Figure 5

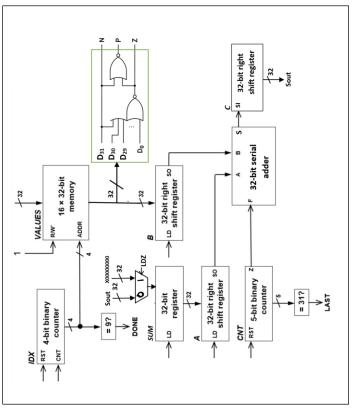

[8 points] Now draw the FSM controller using the expressions you developed and complete the datapath in **Figure 6**. Specifically,

- (a) show the necessary circuits for the next state transitions and connect them to the corresponding FFs,

- (b) label the control signals generated by your FSM-controller, and

- (c) connect the control signals to the corresponding inputs on the datapath.

Figure 6 Datapath

Transition logic DFFs Output logic

### Problem 5 (21 points): LC-3 instructions

The following LC-3 program fragment, represented as three hexadecimal numbers, is stored in memory at the indicated locations and the following values are stored in registers:

| address | instruction |

|---------|-------------|

| xB4FF   | X993F       |

| xB500   | X6503       |

| xB501   | X7903       |

| xB502   | XECEB       |

| register | value |

|----------|-------|

| R0       | xAAAA |

| R1       | xBBBB |

| R2       | xCCCC |

| R3       | X2222 |

| register | value |

|----------|-------|

| R4       | X4B00 |

| R5       | X4B01 |

| R6       | X1111 |

| R7       | X4B03 |

**1. (6 points)** Re-write three instructions in binary representation and provide their corresponding RTL. (*Note: formats of the entire LC-3 instruction set are provided at the end of the exam booklet.)*

| address | instruction | binary instruction | RTL (be specific to this instruction) |

|---------|-------------|--------------------|---------------------------------------|

| xB4FF   | X993F       |                    |                                       |

| xB500   | X6503       |                    |                                       |

| xB501   | X7903       |                    |                                       |

2. (10 points) Assuming PC is initially set to xB4FF, trace the execution of the given program segment for two instruction cycles, filling in the table below. Write down the values stored in the PC, IR, MAR, MDR, N, Z, and P registers at the end of the instruction cycle. Values for PC, IR, MAR, and MDR should be written in hexadecimal. Values for N, Z, and P should be written in binary.

| PC | IR | MAR | MDR | N | Z | P |

|----|----|-----|-----|---|---|---|

|    |    |     |     |   |   |   |

|    |    |     |     |   |   |   |

|    |    |     |     |   |   |   |

| 3. (1 point) What hexadecimal value will be stored in R2 after the three instruction |

|--------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|

Answer:

**4.** (1 point) What hexadecimal value will be stored at address xB502 after the three instruction cycle??

Answer:

**5. (3 point)** Add an instruction at address xB503 such that value xDDDD will be stored at R5 after the instruction cycle. You will need the information that xDDDD is not located anywhere in memory. Write your answer in hexadecimal.

| Answer: |  |  |

|---------|--|--|

|         |  |  |

#### **Appendix:**

Figure 7 Datapath

VALUES – it is a 16x32 memory to hold the ten integer values of the array, values[]. We assume that the memory was filled in with the 10 integer values by some external device before the FSM start processing the data. The external device generates START signal (not shown here) to let the FSM know that the memory has been filled in with 10 integer values. The R/W' is set to 1 to enable memory read mode during the operation of the FSM. values[idx] refers to the memory element at the current memory location/address.

IDX – is a 4-bit counter. The counter output is used as the address line for the memory to read ten integer values in order. The **DONE** signal generated by the counter is used to indicate whether the FSM has processed ten integer values of the array.

Control signals: IDX.RST is used to reset the counter to zero. IDX.CNT is used to increment the counter. When IDX.CNT is 1, the counter is incremented by 1 with the rising edge of the clock. CNT – is a 5-bit counter. It is used to count whether the serial adder has completed processing 32 pairs of bits of shift registers A and B. The **LAST** signal becomes 1 when the serial adder has received the last pair of bits of A and B. The counter is initialized to zero at the beginning of every serial addition process (i.e. when the shift registers A and B are loaded with two integer values to be added by the 32-bit serial adder). It generates a signal, Z=1, when the counter is reset to zero, to indicate that the first pair of bits of A and B have arrived at the serial adder. Otherwise, Z will be set to 0.

Control signals: CNT.RST =1 is used to reset the counter to zero. Otherwise, the counter is incremented by 1 with every rising of the clock.

NPZ – is used to indicate whether the value at the current memory address/location, i.e. values[idx] is negative, positive or zero.

SUM – is a 32-bit register that will hold the summation of the positive integers of the array. The SUM is connected to a multiplexer so that it can be initialized to zeros, or it can be loaded with the Sout (i.e. sum+values[idx]) during the execution of FSM. Note: SUM will hold the result only for one cycle after the COPY state.

Control signal: LD signal along with the multiplexer selection input LDZ are used to initialize the register or to load the current sum into the register.

**A, B, and C** – are 32-bit right shift registers. A and B are connected to the serial inputs of the 32-bit serial adder and C is connected to the output of the serial adder. Control signals LD.A and LD.B are used to load A with SUM, and B with values[idx] respectively. Serial adder output S is connected to the SI (serial Input) of C, which stores the results of serial addition. Note: **Sout** will have the result of 32-bit serial addition in the next cycle when **LAST** signal becomes 1 (i.e. after 32 pairs of bits of A and B have been processed in the serial adder).

Table of ASCII Characters

| Char  | Dec | Hex | ı | Char | Dec | Hex | ı | Char | Dec | Hex | ı | Char  | Dec | Hex |

|-------|-----|-----|---|------|-----|-----|---|------|-----|-----|---|-------|-----|-----|

| (nul) | 0   | 00  | i | (sp) | 32  | 20  | İ | @    | 64  | 40  | ĺ | `     | 96  | 60  |

| (soh) | 1   | 01  | Ì | !    | 33  | 21  | ĺ | A    | 65  | 41  | ĺ | a     | 97  | 61  |

| (stx) | 2   | 02  | Ì | **   | 34  | 22  | ĺ | В    | 66  | 42  | ĺ | b     | 98  | 62  |

| (etx) | 3   | 03  |   | #    | 35  | 23  |   | С    | 67  | 43  |   | С     | 99  | 63  |

| (eot) | 4   | 04  | ı | \$   | 36  | 24  |   | D    | 68  | 44  | - | d     | 100 | 64  |

| (enq) | 5   | 05  | Ì | 용    | 37  | 25  | ĺ | E    | 69  | 45  | ĺ | е     | 101 | 65  |

| (ack) | 6   | 06  | Ī | &    | 38  | 26  | ĺ | F    | 70  | 46  | ĺ | f     | 102 | 66  |

| (bel) | 7   | 07  |   | •    | 39  | 27  |   | G    | 71  | 47  |   | g     | 103 | 67  |

| (bs)  | 8   | 08  |   | (    | 40  | 28  |   | Н    | 72  | 48  |   | h     | 104 | 68  |

| (ht)  | 9   | 09  |   | )    | 41  | 29  |   | I    | 73  | 49  |   | i     | 105 | 69  |

| (lf)  | 10  | 0a  |   | *    | 42  | 2a  |   | J    | 74  | 4a  |   | j     | 106 | 6a  |

| (vt)  | 11  | 0b  |   | +    | 43  | 2b  |   | K    | 75  | 4b  |   | k     | 107 | 6b  |

| (ff)  | 12  | 0c  |   | ,    | 44  | 2c  |   | L    | 76  | 4c  |   | 1     | 108 | 6c  |

| (cr)  | 13  | 0d  |   | -    | 45  | 2d  |   | M    | 77  | 4 d |   | m     | 109 | 6d  |

| (so)  | 14  | 0e  |   |      | 46  | 2e  |   | N    | 78  | 4e  |   | n     | 110 | 6e  |

| (si)  | 15  | 0f  |   | /    | 47  | 2f  |   | 0    | 79  | 4 f |   | 0     | 111 | 6f  |

| (dle) | 16  | 10  |   | 0    | 48  | 30  |   | P    | 80  | 50  |   | р     | 112 | 70  |

| (dc1) | 17  | 11  |   | 1    | 49  | 31  |   | Q    | 81  | 51  |   | q     | 113 | 71  |

| (dc2) | 18  | 12  |   | 2    | 50  | 32  |   | R    | 82  | 52  |   | r     | 114 | 72  |

| (dc3) | 19  | 13  |   | 3    | 51  | 33  |   | S    | 83  | 53  |   | s     | 115 | 73  |

| (dc4) | 20  | 14  |   | 4    | 52  | 34  |   | T    | 84  | 54  |   | t     | 116 | 74  |

| (nak) | 21  | 15  |   | 5    | 53  | 35  |   | U    | 85  | 55  |   | u     | 117 | 75  |

| (syn) | 22  | 16  |   | 6    | 54  | 36  |   | V    | 86  | 56  |   | V     | 118 | 76  |

| (etb) | 23  | 17  |   | 7    | 55  | 37  |   | W    | 87  | 57  |   | W     | 119 | 77  |

| (can) | 24  | 18  |   | 8    | 56  | 38  |   | Χ    | 88  | 58  |   | X     | 120 | 78  |

| (em)  | 25  | 19  |   | 9    | 57  | 39  |   | Y    | 89  | 59  |   | У     | 121 | 79  |

| (sub) | 26  | 1a  |   | :    | 58  | 3a  |   | Z    | 90  | 5a  |   | Z     | 122 | 7a  |

| (esc) | 27  | 1b  |   | ;    | 59  | 3b  |   | [    | 91  | 5b  |   | {     | 123 | 7b  |

| (fs)  | 28  | 1c  |   | <    | 60  | 3с  |   | \    | 92  | 5с  |   |       | 124 | 7с  |

| (gs)  | 29  | 1d  |   | =    | 61  | 3d  |   | ]    | 93  | 5d  |   | }     | 125 | 7d  |

| (rs)  | 30  | 1e  |   | >    | 62  | 3e  |   | ^    | 94  | 5e  |   | ~     | 126 | 7e  |

| (us)  | 31  | 1f  |   | ?    | 63  | 3f  |   |      | 95  | 5f  |   | (del) | 127 | 7f  |