# ECE 120 Third Midterm Exam Spring 2017

Tuesday, April 18, 2017

| Name: SOU             | TIONS                  | NetID:         |  |

|-----------------------|------------------------|----------------|--|

| Discussion Section ar | nd TA name:            | 1              |  |

| 9:00 AM               | [ ] AB1 Rui            |                |  |

| 10:00 AM              | [ ] AB2 Rui            |                |  |

| 11:00 AM              | [ ] AB3 Matt           |                |  |

| 12:00 PM              | [ ] AB4 Pawel          |                |  |

| 1:00 PM               | [ ] AB5 Pawel          |                |  |

| 2:00 PM               | [ ] AB6 Gowthami       | [ ] ABA Huiren |  |

| 3:00 PM               | [ ] AB7 Gowthami       | [ ] ABB Huiren |  |

| 4:00 PM               | [ ] AB8 Yu-Hsuan       | [ ] ABC Sifan  |  |

| 5:00 PM               | [ ] AB9 Yu-Hsuan       | [ ] ABD Surya  |  |

|                       |                        |                |  |

| a Po sure that w      | our exam booklet has 9 |                |  |

- Write your name, netid and check discussion section on the title page.

- Do not tear the exam booklet apart, except for the last two pages.

- Use backs of pages for scratch work if needed.

- This is a closed book exam. You may <u>not</u> use a calculator.

- You are allowed one handwritten 8.5 x 11" sheet of notes (both sides).

- Absolutely no interaction between students is allowed.

- Clearly indicate any assumptions that you make.

- The questions are not weighted equally. Budget your time accordingly.

- Show your work.

|   | Total     | 100 points |  |

|---|-----------|------------|--|

| , |           |            |  |

|   | Problem 5 | 19 points  |  |

|   | Problem 4 | 27 points  |  |

|   | Problem 3 | 22 points  |  |

|   | Problem 2 | 16 points  |  |

|   | Problem 1 | 16 points  |  |

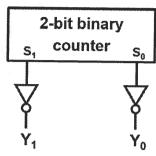

# Problem 1 (16 points): Counter Design

Q

The FSM drawn below consists of a 2-bit binary counter ( $S_1S_0$  counts 0, 1, 2, 3, then returns to 0) and two inverters.

1. (8 points) Draw a state transition diagram for the FSM. Label each node with the state identifier  $S_1S_0$  and the output  $Y_1Y_0$ . Do not cross transition arcs.

2. (5 points) In TEN OR FEWER words, what does the FSM do? Hint: Look at the output sequence.

Courts downward: 3, 2, 1, 0, respect

**3. (3 points)** In the design above, the counter is treated as a black box—in other words, only the outputs S<sub>1</sub> and S<sub>0</sub> are available. If instead you had access to all transistors in the 2-bit binary counter design (that produces S<sub>1</sub>S<sub>0</sub>), what is the minimum number of additional transistors needed to implement the FSM that produces Y<sub>1</sub>Y<sub>0</sub>?

Minimum number of additional transistors = ( autputs of flip-flops)

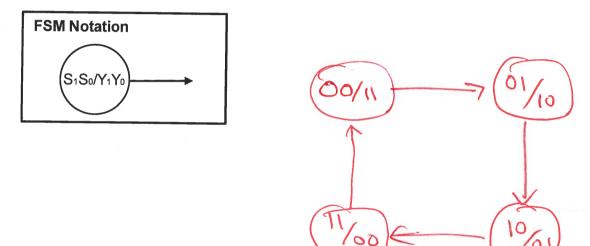

# Problem 2 (16 points): Sequence Recognizer

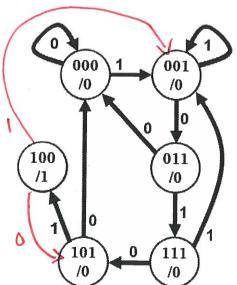

Consider the state transition diagram shown below. Nodes are labeled with the state  $S_2S_1S_0$  and the output R. Transition arcs are labeled with input B. **Assume that the FSM starts in state**  $S_2S_1S_0$ =000.

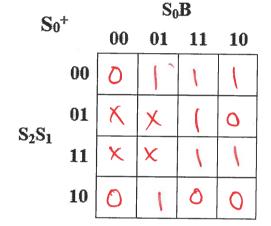

- (8 points) Fill in the K-map to the right for the next state bit S<sub>0</sub><sup>+</sup> as a function of the current state S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> and the input B.

- 2. (8 points) The above FSM implements a sequence recognizer for non-overlapping instances of the sequence 10101. For example, if the FSM receives the input sequence 1010101, it produces the output sequence 0000100.

The figure to the right is the same as the one above, except that the two transitions coming from state 100 have been removed.

**Draw and label the transitions from state 100** so that the resulting FSM recognizes overlapping instances of the sequence 10101. That is, if the FSM receives the input sequence 1010101, it produces the output sequence 0000101.

#### Problem 3 (22 points): Memory

W

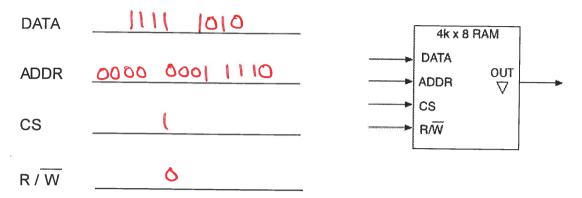

(10 points) The figure below shows the block diagram of a 4k x 8-bit RAM chip. Recall that 1k = 1024. Provide inputs to the RAM in order to store the decimal value -6 in location (decimal) 30. Answer in binary with the <u>correct number of bits</u>.

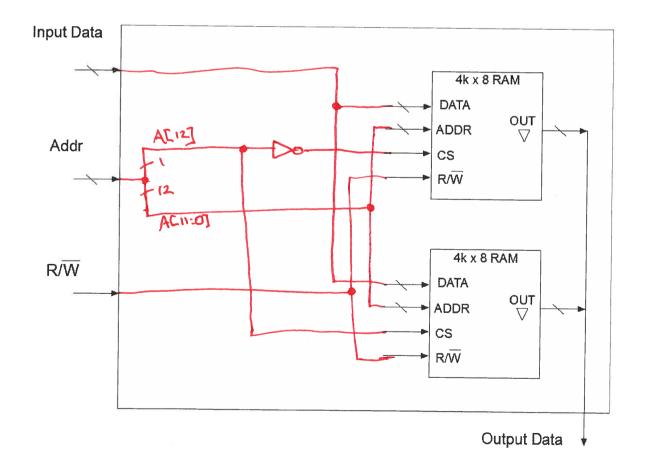

2. (12 points) Use two of these 4k x 8-bit RAM chips (with CS) to build an 8k x 8-bit RAM (without CS). Draw wires to complete the logic below. The Output Data lines have been drawn for you. You may use at most one additional gate (AND, OR, or NOT). Label wires as needed (for example, Addr[3:0]) and write the number of wires wherever a "slash" is drawn.

#### Problem 4 (27 points): FSM Design

The city of Urbana has the following traffic light controller:

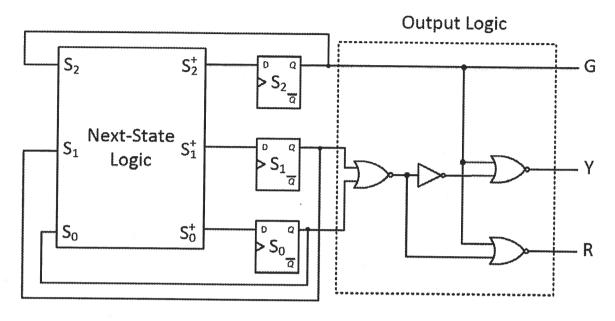

The next-state logic guarantees that the **FSM** is a 3-bit binary up-counter ( $S_2S_1S_0$  counts the sequence 0, 1, 2, ..., 7, 0, 1, 2, ...), while the output logic translates the current state  $S_2S_1S_0$  into outputs for the three lights: G (green), Y (yellow), and R (red).

The mayor of Urbana has requested the help of the ECE Department to extend the design to cope with emergency vehicles (fire engines, ambulances, police, and so forth.) Since the ECE 120 instructors are *very* busy, and the timing for midterm 3 was just perfect, your task is to extend the FSM as follows:

- 1. When an emergency vehicle nears the traffic light, your extended FSM receives a new input **E=1** (otherwise, input E=0).

- a) If the **red light is lit (R=1)**, the FSM should **hold its current state** until E returns to 0 (after the emergency vehicle has passed).

- b) If the **yellow light is lit (Y=1)**, the FSM should **continue to advance** in the same way as in the original design.

- c) If the **green light is lit (G=1)**, the extended FSM must **light the yellow light (Y=1)** in the next cycle. (Safety is of utmost concern to the mayor. We don't want vehicles to suddenly stop and crash!)

- 2. If no emergency vehicle is present (**E=0**), the extended design should **continue to** advance in the same way as the original design behaved.

(The questions you need to answer are on the next page.)

# Problem 4 (27 points): FSM Design, continued

1. (18 points) Write the state transition table for the extended design.

| Ct             | ırrent St      | ate            | Input |                  | Next Sta | te                          | T | Outputs | 3        |

|----------------|----------------|----------------|-------|------------------|----------|-----------------------------|---|---------|----------|

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Е     | S <sub>2</sub> + | S₁⁺      | S <sub>0</sub> <sup>+</sup> | G | Y       | R        |

| 0              | 0              | 0              | 0     | 0                | 0        | 1                           | 0 |         | 3        |

| 0              | 0              | 1              | 0     | 0                | (        | 0                           | 6 | ٥       | 1        |

| 0              | 1              | 0              | 0     | O                | (        | 1                           | 0 | O       | <u>'</u> |

| 0              | 1              | 1              | 0     | 1                | 0        | 0                           | 0 | ٥       | 1        |

| 1              | 0              | 0              | 0     |                  | 0        | (                           |   | O       | 6        |

| 1              | 0              | 1              | 0     | 1                | Ţ        | 0                           | 1 | U       | 0        |

| 1              | 1              | 0              | 0     | (                | (        | - (                         | 1 | 0       | 0        |

| 1              | 1              | 1              | 0     | 0                | 0        | 0                           | 1 | 0       | 0        |

| 0              | 0              | 0              | .1    | O                | 0        | <b>1</b>                    | O |         | G        |

| 0              | 0              | 1              | 1     | 0                | 0        | 1                           | U | · ·     | 1        |

| 0              | 1              | 0              | 1     | 0                | 1        | 0                           | O | O O     |          |

| 0              | 1              | 1              | 1     | 0                |          | )                           | U | 2       | ,        |

| 1              | 0              | 0              | 1     | 0                | 0        | 0                           |   | C       | 0        |

| 1              | 0              | 1              | 1     | 0                | 0        | 0                           | 1 | C       | 0        |

| 1              | 1              | 0              | 1     | 9                | 0        | 0                           |   | U       | v        |

| 1              | 1              | 1              | 1     | 0                | 0        | 0                           |   | O       | 0        |

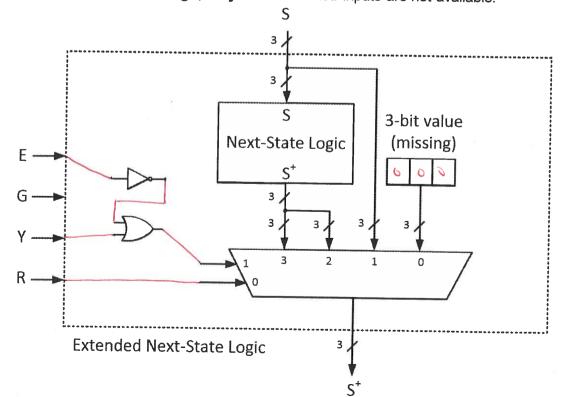

- 2. (9 points) The circuit below extends the next-state logic as specified in the previous page to cope with the new input E, but it has not been finished yet.

- a. Write the missing 3-bit value in the provided boxes.

- b. Finish the design by drawing the missing wires. You are NOT allowed to add any other component to the design, only wires. Inverted inputs are not available.

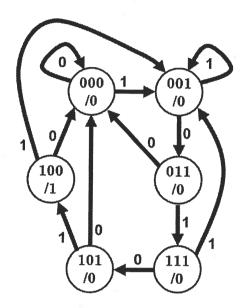

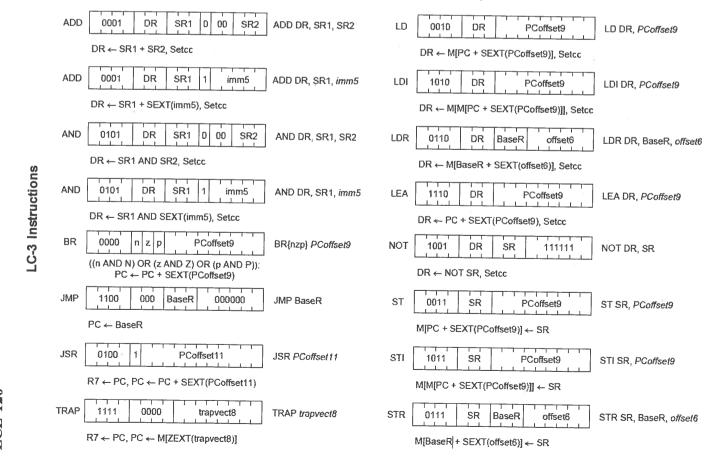

# Problem 5 (19 points): LC-3 Interpretation and Assembly

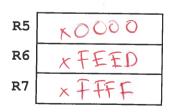

The registers of an LC-3 processor currently have the values shown in the table to the right.

| R0 | x0000 |

|----|-------|

| R1 | x1111 |

| R2 | x2222 |

| R3 | x3333 |

| R4 | x4444 |

|----|-------|

| R5 | x5555 |

| R6 | x6666 |

| R7 | xFFFF |

|    |       |

| PC  | x4401 |

|-----|-------|

| IR  | x11E1 |

| MAR | x4400 |

| MDR | x11E1 |

The table to the right shows some of the contents of the LC-3 processor's memory.

When the bits represent instructions, an interpretation has been provided for you in RTL.

| address | contents            | RTL interpretation |

|---------|---------------------|--------------------|

| x4400   | 1                   | R0 ← R7+1          |

| x4401   | 1001 101 111 111111 | R5 ← NOT (R7)      |

| x4402   |                     | R6 ← M[R4+1]       |

| x4403   | 1011 111 001000000  | M[M[PC+x040]]←R7   |

| ~4443 i | 0100 0100 0100 0101 | •••                |

|       | • • •               |               |

|-------|---------------------|---------------|

|       | 0100 0100 0100 0101 | (data: x4445) |

| x4444 | 0100 0100 0100 0110 | (data: x4446) |

| x4445 | 1111 1110 1110 1101 | (data: xFEED) |

| x4446 | 1110 1100 1110 1011 | (data: xECEB) |

# Here's the question:

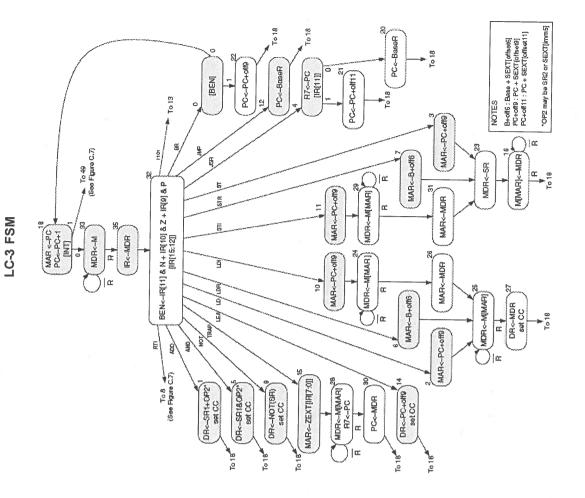

The LC-3 FSM PROCESSES THREE INSTRUCTIONS, starting with the fetch phase.

1. (7 points) Write a complete list of the sequence of values taken by the MAR register as the LC-3 processes these instructions. Use only as many lines as are necessary.

#1: <u>x4400 (initial value)</u>

#2: <u>X 4 4 0 1</u>

#3: <u>X 44 0 2</u>

#5: <u>×4403</u> #6: <u>×4444</u> #7: <u>×4446</u>

#8:

2. (12 points) Complete the tables below with the FINAL values (after processing of three instructions) of each register and memory location. To receive credit, you must write your answers in hexadecimal.

PC x4404

IR xBE40

MDR x FFFF

| memory address | contents |

|----------------|----------|

| x4443          | ×4445    |

| x4444          | × 4446   |

| x4445          | X FEED   |

| x4446          | XFFFF    |

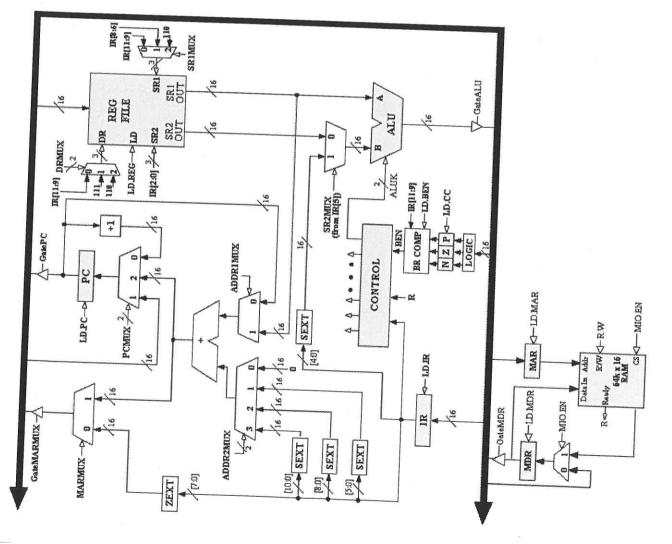

NOTES: RTL corresponds to execution (after fetch!); JSRR not shown

Signal Description Description LD.MAR = 1, MAR is loaded LD.CC = 1, updates status bits from system bus LD.MDR = 1, MDR is loaded LD.IR = 1, IR is loaded GateMARMUX = 1, MARMUX output is put onto system bus LD.PC = 1, PC is loaded GateMDR = 1, MDR contents are put onto system bus = 1, register file is loaded LD.REG GateALU = 1, ALU output is put onto system bus LD.BEN = 1, updates Branch Enable (BEN) bit GatePC = 1, PC contents are put onto system bus = 0, chooses ZEXT IR[7:0] = 1, Enables memory, chooses memory output for MDR input MIO.EN -1, chooses address adder output = 0, Disables memory, chooses system bus for MDR input = 0, chooses PC = 1, chooses reg file SR1 OUT ADDR1MUX = 1, M[MAR]<-MDR when MIO.EN = 1 = 0, MDR<-M[MAR] when MIO.EN = 1 = 00, chooses "0...00" = 01, chooses SEXT IR[5:0] = 10, chooses SEXT IR[8:0] = 11, chooses SEXT IR[10:0] = 00, ADD ADDR2MUX « = 01, AND = 10, NOT A = 11, PASS A = 00, chooses PC + 1 = 01, chooses system bus  $DRMUX \begin{cases} = 00, \text{ chooses } IR[11:9] \\ = 01, \text{ chooses } "111" \end{cases}$ = 10. chooses address adder output = 10, chooses "110" = 00, chooses IR[11:9] = 01, chooses IR[8:6] SR1MUX ₹ = 10, chooses "110"